#### FCCM 2023

## OFS on Intel Stratix 10

John Tio Application Engineer

## Agenda

- Overview

- BMC

- FIM

- OPAE-SDK

- OFS Development

- AFU Development

- AFU Simulation Environment

- Summary

#### intel

3

Software Development

Intel<sup>®</sup> Open **FPGA Stack**

Hardware

Development

Application

evelopment

#### Growing ecosystem of OFS-enabled boards, workloads, and OS distributions

interfaces and by deploying across multiple OFS-based platforms

#### vendors Maximize ROI for workload developers with standard hardware and software

- Reduce development time with modular and composable source code used as-is or easily customized

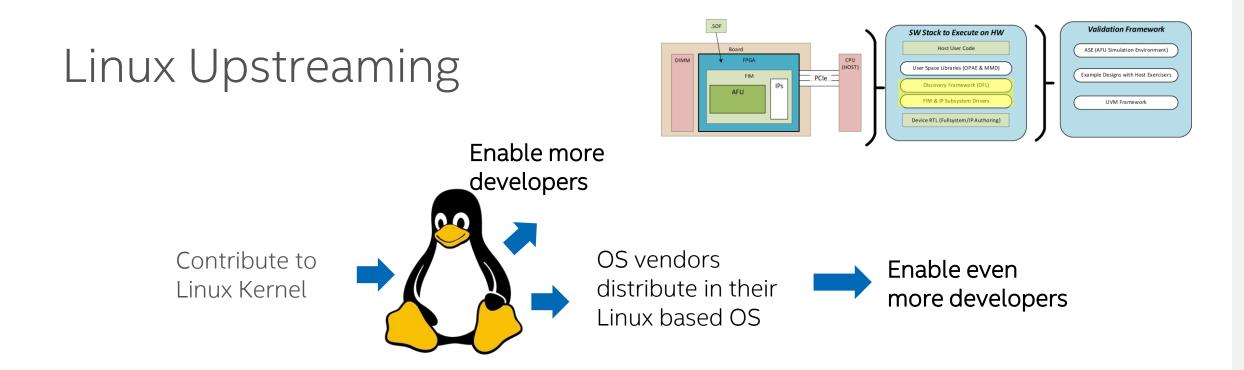

- Upstreamed Linux kernel drivers are being adopted by leading OS and orchestration

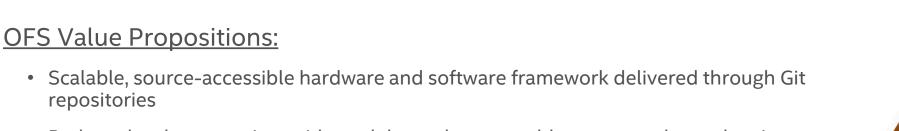

OFS is a **software and hardware infrastructure** providing an efficient path to develop a custom FPGA-based platform or workload using an Intel, 3rd party, or custom board.

### What is OFS?

repositories

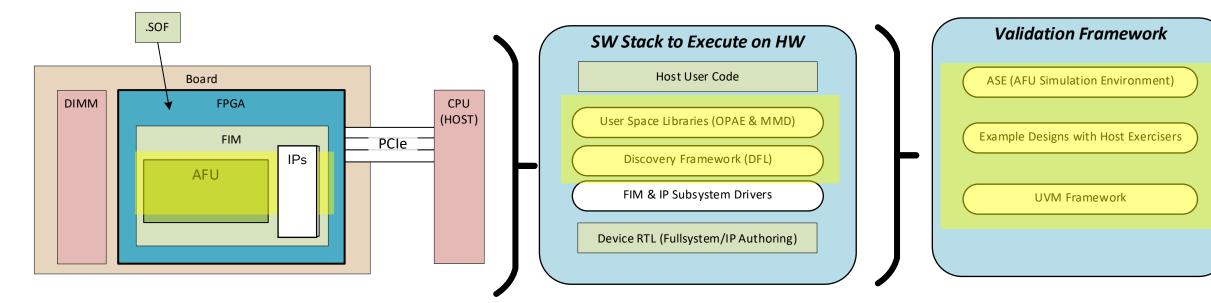

## OFS Deliverables

#### Hardware

- Acceleration Functional Unit (AFU) Region for Workload Development with Sample AFUs

- FPGA Interface Manager (FIM)

- Board Management Controller (BMC)

- HLD enablement

#### Software

- Upstreamed, open-source kernel drivers

- OPAE libraries, tools and APIs

- Example Applications

#### **Verification Environment**

UVM Verification environment provided through Git repositories

### **Developer Benefits**

#### Software Developer

- Utilize open-sourced and upstreamed kernel drivers and user space

- Flexibility to target OS distributions of choice \*or\*

- Native support from leading vendor OS distributions

#### Hardware/Board Developer

- Leverage source-accessible, modular RTL source code

- Easily modify or use as-is in the provided framework to save development time

#### **Application Developer**

- Develop applications in RTL or HLD (OpenCL/oneAPI) for increased portability and ROI across OFS-based platforms

- Leverage a growing ecosystem of OFS-based platforms from Intel and third-parties

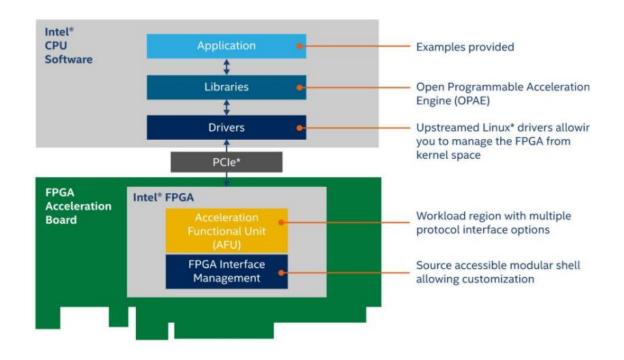

### OFS Enables Scale and Deployment

| Scalable infrastructure                                                                             |

|-----------------------------------------------------------------------------------------------------|

| <ul> <li>Addressing needs of board, software and application developers</li> </ul>                  |

| <ul> <li>Source-accessible hardware and software code for BMC, FIM and related IP blocks</li> </ul> |

| Customize your platform                                                                             |

| <ul> <li>Modular and composable source code</li> </ul>                                              |

| <ul> <li>Take and tailor Intel supplied IP to meet platform needs</li> </ul>                        |

| Adoption of upstreamed kernel code                                                                  |

| <ul> <li>Leading OS and orchestration vendor support</li> </ul>                                     |

| Growing ecosystem                                                                                   |

| <ul> <li>Intel<sup>®</sup> Open FPGA Stack-based boards from Intel and third parties</li> </ul>     |

| <ul> <li>Portable RTL and HLD-based accelerator workloads</li> </ul>                                |

| <ul> <li>Flexibility for OS distributions and orchestration frameworks</li> </ul>                   |

|                                                                                                     |

|                                                                                                     |

| OFS Deliverable                                                                                     |

Intel or Third Party Third Party

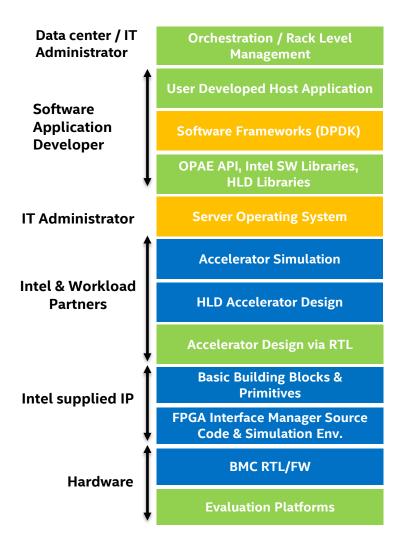

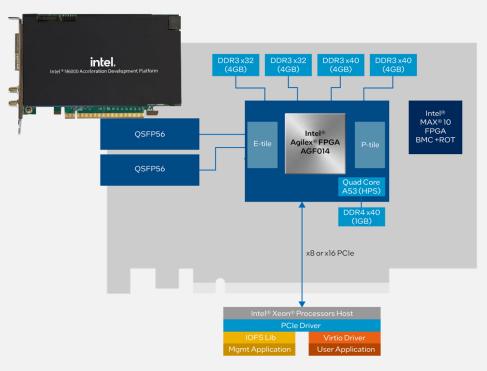

#### OFS Reference Platforms

Leverage hardware reference platforms as a starting point for evaluating OFS

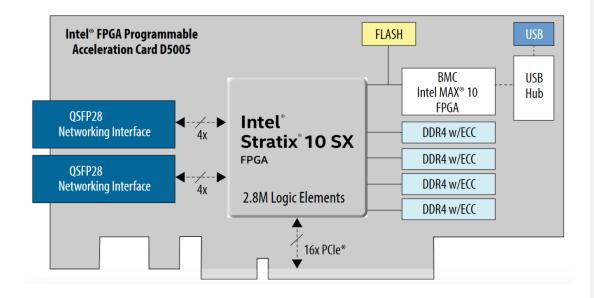

Intel Stratix 10: D5005 Programmable Acceleration Platform (PAC)

#### Agilex:N600x Acceleration Development Platform (ADP)

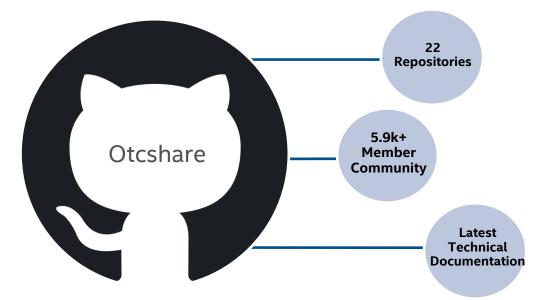

### Open-Source Development Methodology

- Source-accessible hardware code for Stratix 10 and Agilex delivered to community through Git repositories

- Hardware source code access must be requested through an Intel representative

- Working towards a fully open-sourced model incorporating code contributions

- Intel Stratix 10 code (<u>https://github.com/OFS</u>) is available today in Github

- Open-source software code (<u>https://github.com/OPAE</u>) is available today on Github

- Kernel drivers are currently being upstreamed to kernel.org with patches

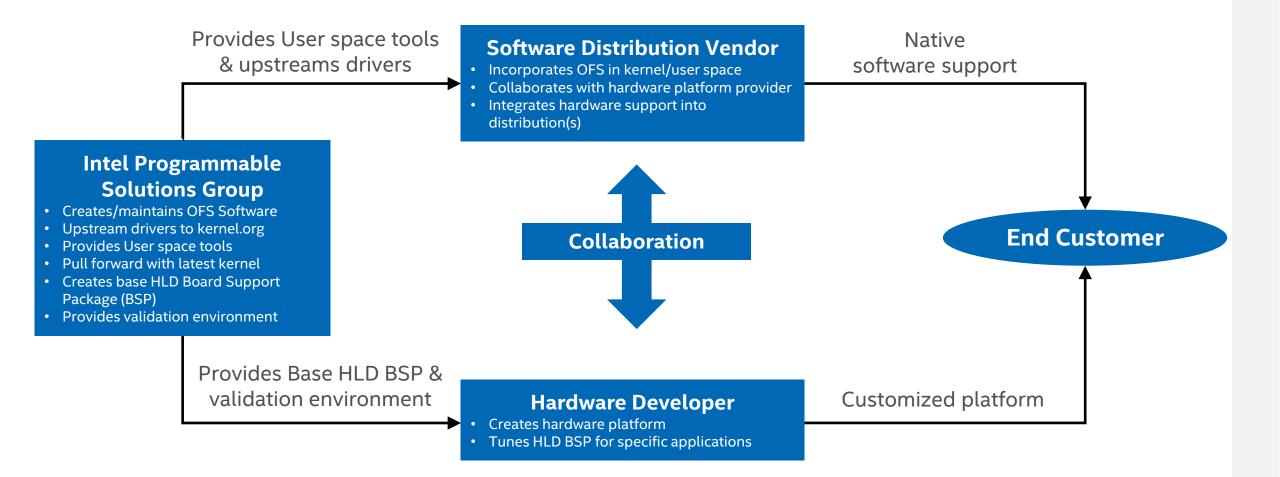

#### Software Collaboration Model

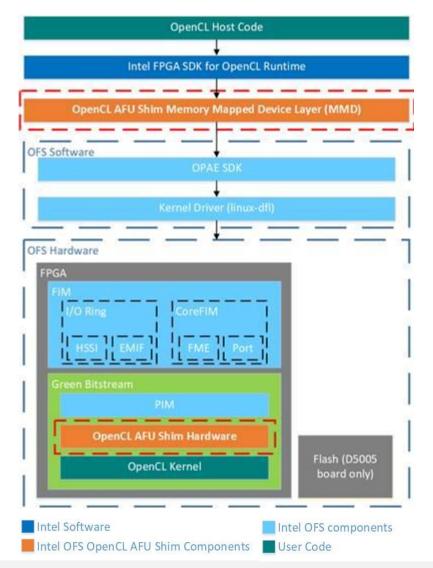

#### Develop HLD Applications using OpenCL & oneAPI

- OFS HLD Shim enables compilation/running of OpenCL kernels on OFS platforms

- Compatible with existing high-performance languages

- Leverage familiar programming languages to improve rampup and debug time

- OpenCL & oneAPI development on OFS enables <u>portability</u> across architectures and board vendors

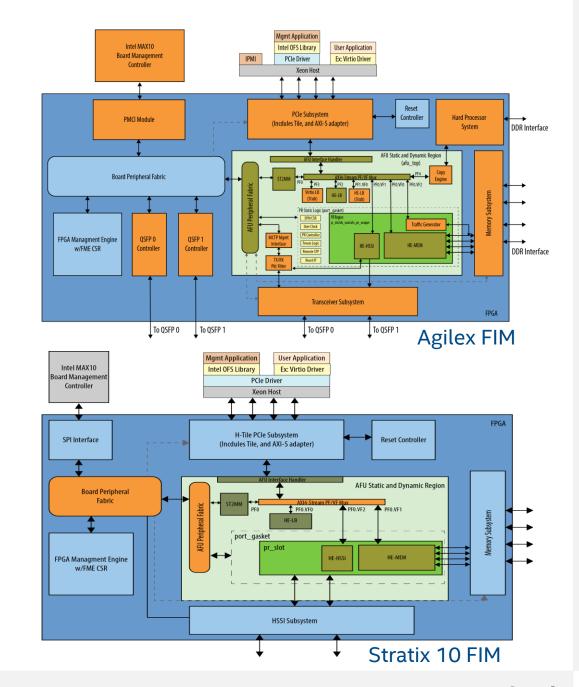

#### OFS Base FIMs

#### Leverage the base FIM as-is or modify it to reduce development time

| Key Feature                       | Stratix 10 Reference FIM                                                | Agilex Reference FIM                                   |  |

|-----------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------|--|

| FPGA                              | Intel <sup>®</sup> Stratix <sup>®</sup> 10 SX FPGA                      | Intel® Agilex™ FPGA                                    |  |

| Processor                         | Device contains HPS with Arm <sup>®</sup> but is not pinned out on card | HPS with Arm <sup>®</sup> Cortex A-53                  |  |

| Ethernet<br>Configuration         | 1x10 GbE                                                                | 2x4x25 GbE                                             |  |

| PCle                              | Gen 3x16                                                                | Gen 4x16                                               |  |

| EMIF                              | Up to 4 DDR4 channels                                                   | Up to 4 DDR4 channels and 1 HPS<br>Channel: 1 x40, 2GB |  |

| PF/VF                             | 1 PF / 3 VFs                                                            | 5 PFs / 4 VFs                                          |  |

| Management                        | FPGA Management Engine (FME) with FIM management registers              |                                                        |  |

| Interface                         | AXI4                                                                    |                                                        |  |

| HLD Support                       | oneAPI*                                                                 |                                                        |  |

| Board<br>Management<br>Controller | MAX 10 BMC                                                              | New, Enhanced MAX 10 BMC<br>Architecture               |  |

| UVM                               | UVM Support for FIM and AFU                                             |                                                        |  |

| Software                          | Kernel code upstreamed to Linux                                         |                                                        |  |

#### AFU Development

- Focused on the algorithm

- Can be PR

- Scripts provided for SW/HW co-simulation and synthesis

- Uses PR Template generated by FIM build script

- Developer specifies environment variable to point to required FIM qdb files

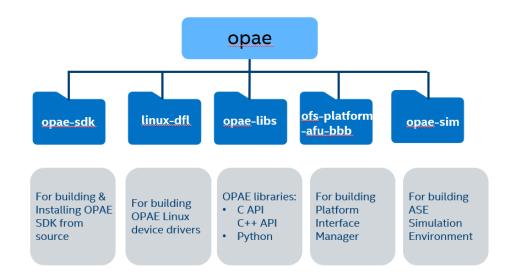

### Repository Folder

| <b>Repository Folder</b> | Description                                                                                                                                                                                               | Hardware or Software Repository |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| linux-dfl                | This repository is a mirror of the linux.org Git site and contains the most up-to-date drivers that are being developed and upstreamed for OFS platforms.                                                 | Software                        |

| opae-sdk                 | Contains the ingredients to build the OFS Open Programmable Acceleration Engine (OPAE)<br>Software Development Kit which provides APIs and userspace tools for OFS FPGA management.                       | Software                        |

| ofs.github.io            | Contains the hardware and software collateral that surfaces on the OFS website: https://ofs.github.io                                                                                                     | Markdown/HTML                   |

| ofs-d5005                | Provides RTL, unit tests, and build scripts to create Intel Stratix 10 FIM and is leveraged as a starting point for a custom design. The reference FIM targets an Intel FPGA PAC D5005 development board. |                                 |

| ofs-fim-common           | Provides RTL components that are shared among all new platforms that are introduced in OFS. Hardware This folder is a subumodule in each platform repository folder.                                      |                                 |

| ofs-platform-afu-bbb     | Contains the hardware and software code used to build the host interface for the FIM and Hardware/Software provides test examples.                                                                        |                                 |

| linux-dfl-backport       | A place for finding and leveraging out-of-tree backported drivers for older OS versions . Software                                                                                                        |                                 |

| examples-afu             | Provides standard AFU examples you can use as a template for starting your own workload design.                                                                                                           | Software                        |

| opae-legacy              | Supports OFS platforms built on the legacy version of OPAE software. Not used in current OFS designs                                                                                                      |                                 |

| opae-sim                 | This repository is used to build the AFU Hardware/Software Co-Simulation Environment Hardrware/Software workload developers can use to ensure their AFU can work with the OFS software stack.             |                                 |

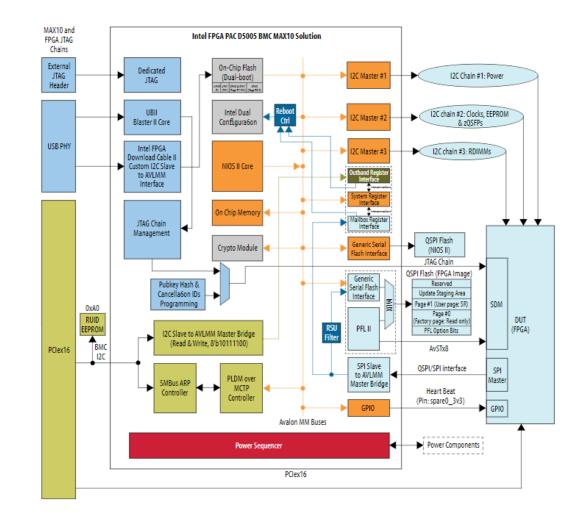

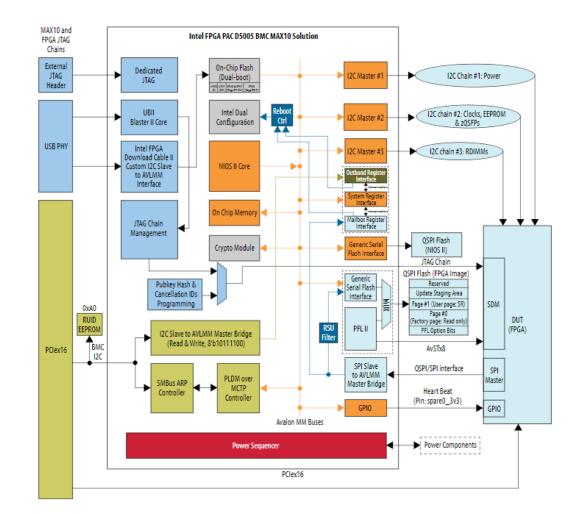

# OFS-BMC

#### Overview

- An Intel<sup>®</sup> MAX<sup>®</sup> 10 FPGA contains the Board Management Controller (BMC) for the Intel FPGA Programmable Acceleration Card D5005.

- The BMC acts as Root of Trust (RoT) on the Intel<sup>®</sup> FPGA PAC D5005.

- The Intel<sup>®</sup> FPGA PAC D5005 BMC supports features

- Power sequence management

- Board monitoring through sensors.

- Secure remote system update for Nios firmware, Intel<sup>®</sup> MAX<sup>®</sup> 10 image and FPGA Interface Manager (FIM) image updates.

## Root of Trust (RoT)

The Intel<sup>®</sup> MAX<sup>®</sup> 10 BMC acts as a Root of Trust (RoT) and enables the secure remote system update feature of the Intel<sup>®</sup> FPGA PAC D5005. The RoT includes features that may help prevent the following:

- Loading unauthorized bitstreams.

- Disruptive operations attempted by unprivileged software, privileged software, or the host BMC.

- Unintended execution of older designs with known bugs or vulnerabilities by enabling the BMC to revoke authorization.

The Intel<sup>®</sup> FPGA PAC D5005 BMC also enforces several other security policies relating to access through various interfaces, as well as protecting the on-board flash through write rate limitation.

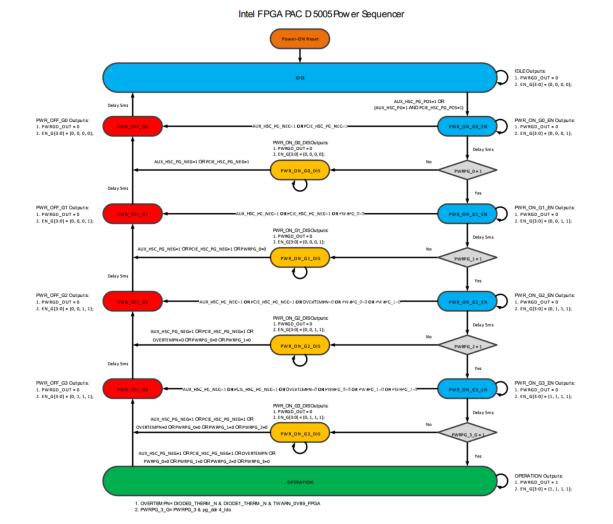

#### Power Sequence Management

- The BMC Power sequencer state machine is used to manage programmable acceleration card power-on and power-off sequences, to handle different corner cases during power-on process or normal operation.

- Intel<sup>®</sup> MAX<sup>®</sup> 10 power-up flow covers the entire process including Intel<sup>®</sup> MAX<sup>®</sup> 10 boot-up, Nios<sup>®</sup> II boot-up, and power sequence management for FPGA configuration.

- The host needs to check the build versions of both Intel® MAX® 10 and FPGA, and the Nios® II status every time after a power-cycle, and then takes corresponding actions in case the Intel® FPGA PAC D5005 runs into corner cases such as a Intel® MAX® 10/FPGA factory build load failure or Nios® II boot up failure.

### Board Monitoring through Sensor

- The Intel<sup>®</sup> MAX<sup>®</sup> 10 BMC monitors voltage, current and temperature of various components on the Intel<sup>®</sup> FPGA PAC D5005.

- Host BMC can access the telemetry data through PCIe SMBus.

- The PCIe SMBus between the host BMC and Intel<sup>®</sup> FPGA PAC D5005 Intel<sup>®</sup> MAX<sup>®</sup> 10 BMC is shared by both:

- PLDM over MCTP SMBus endpoint

- I2C slave to Avalon-MM interface (read-only).

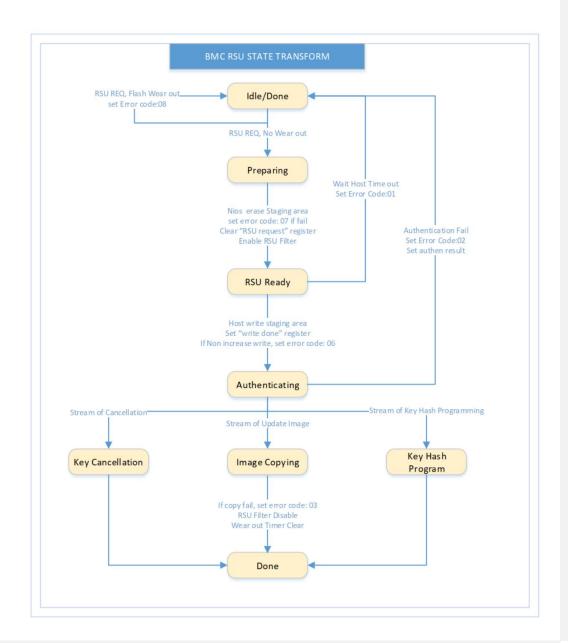

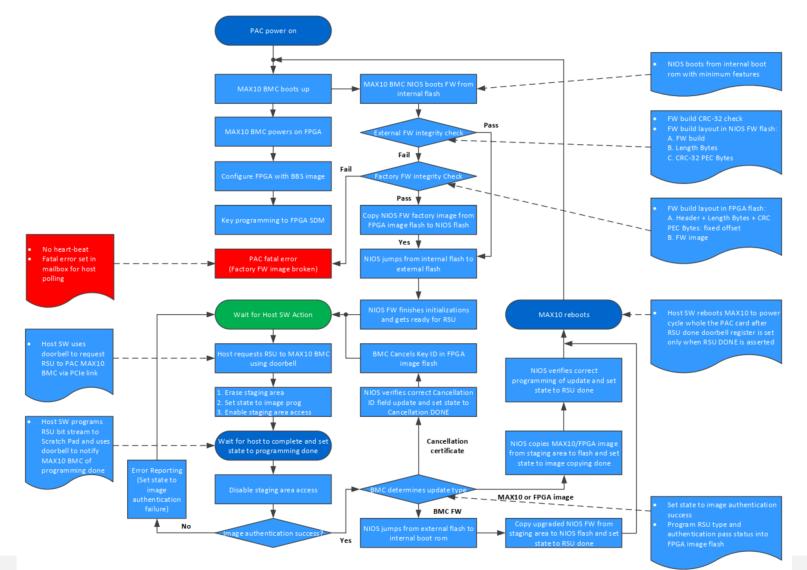

#### Secure Remote System Update

- The Intel® FPGA PAC D5005 provides a mechanism to securely update Nios® II firmware, Intel® MAX® 10 image, or Intel® Stratix® 10 FPGA image over PCIe interface from the host called Remote System Update (RSU). RSU can be used for the following three updates:

- Intel MAX 10 image update

- Nios<sup>®</sup> II firmware image update

- FPGA Interface Manager (FIM) image update

- The Nios<sup>®</sup> II firmware is in charge of authenticating the image during the update process. The updates are pushed over the PCIe interface to the Intel<sup>®</sup> Stratix<sup>®</sup> 10 SX FPGA, which in turn writes to the Intel<sup>®</sup> Stratix<sup>®</sup> 10 FPGA SPI master and finally to the Intel<sup>®</sup> MAX<sup>®</sup> 10 FPGA SPI slave. A temporary flash area called staging area stores any type of authentication bitstream through SPI interface.

- BMC RoT contains the cryptographic module which implements SHA2-256 bit Hash verification function to authenticate the keys and ECDSA-256P-256 signature verification to authenticate your AFU.

- Nios<sup>®</sup> II Firmware uses the cryptographic module to authenticate the user signed image in the staging area, if authentication passes, Nios<sup>®</sup> II Firmware copies the user image to user flash area. If the authentication fails Nios<sup>®</sup> II Firmware reports an error.

#### Remote System Upgrade Flow

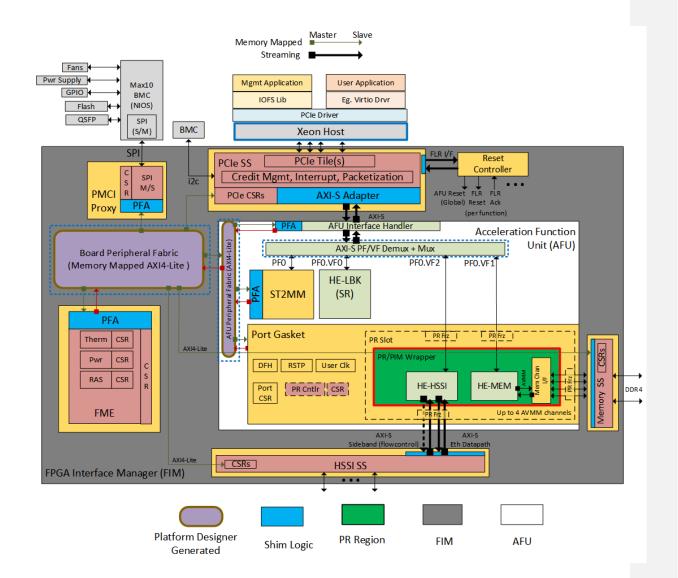

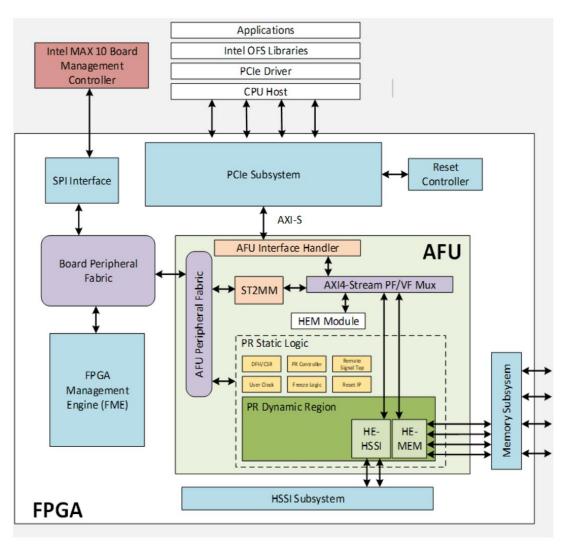

# OFS-FIM

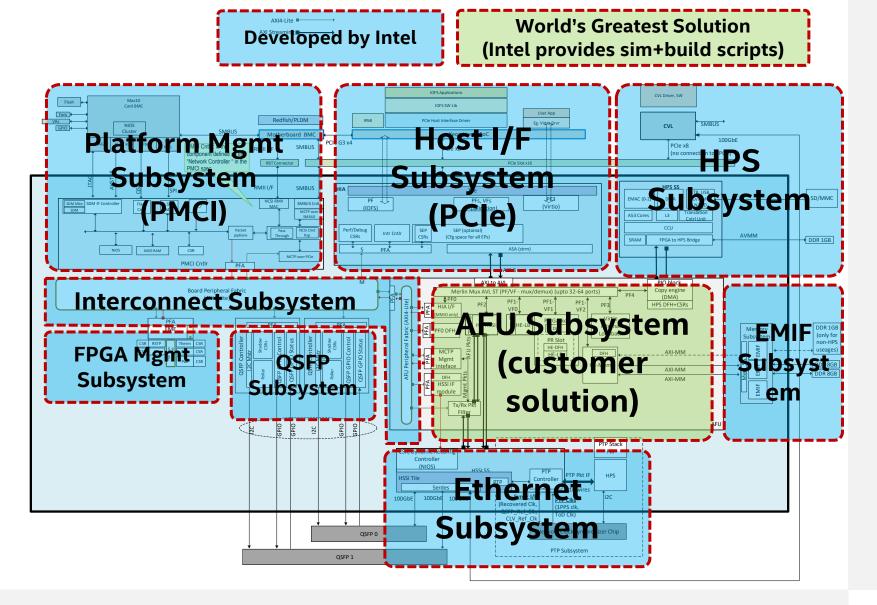

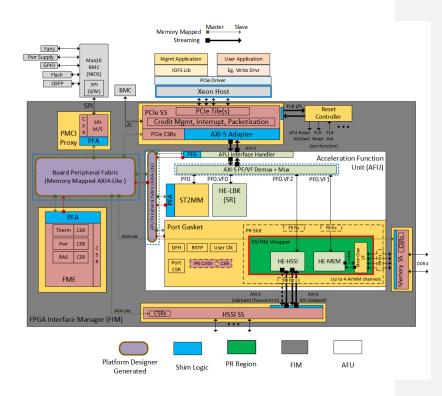

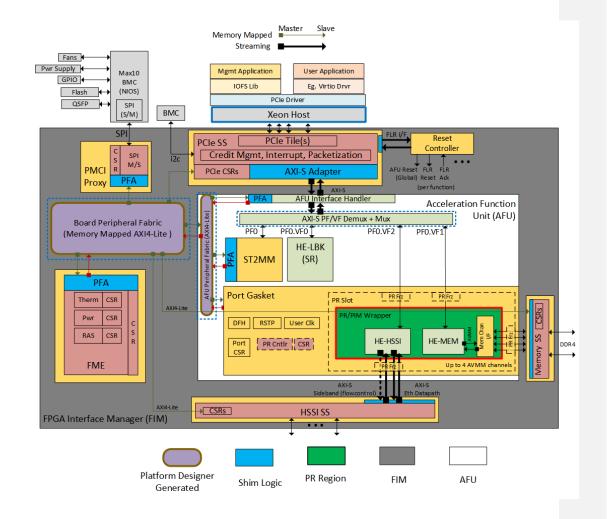

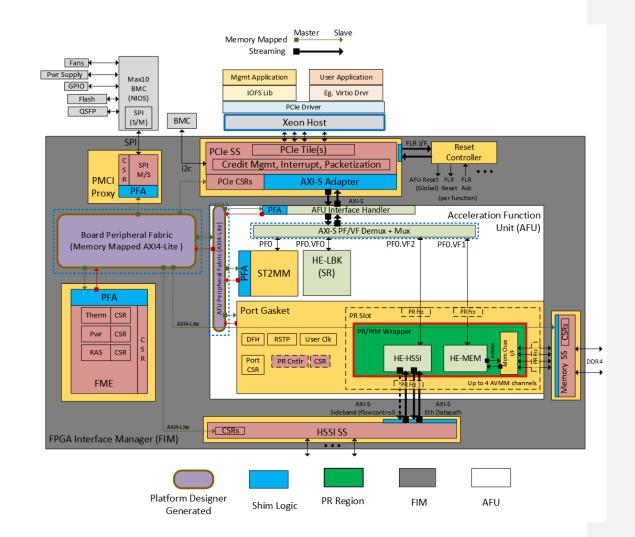

### **OFS** Features

- FPGA Interface Manager (FIM)

- PCIe Subsystem

- HSSI Subsystem

- Memory Subsystem

- Reset Controller

- FPGA Management Engine

- AFU Peripheral Fabric for AFU accesses to other interface peripherals

- Board Peripheral Fabric for master to slave CSR accesses from Host or AFU

- SPI Interface to BMC controller

- Accelerator Functional Unit (AFU)

- Custom workloads and contains both static and partial reconfiguration regions.

#### OFS Features table

| Key Feature               | Description                                                                                                                                                                                            |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PCle                      | H-tile PCIe Gen3x16 Interface                                                                                                                                                                          |  |

| Memory                    | Two Avalon Memory Mapped channels provided as default with capability to compile design with four channels support.                                                                                    |  |

| HSSI                      | 1 Arm* AMBA* 4 AXI4-Stream channel of 10G Ethernet, using the low latency Ethernet 10G MAC Intel FPGA IP interfacing to an E-tile PHY.                                                                 |  |

| Manageability             | SPI interface to Board Management Controller targeting Intel FPGA PAC D5005                                                                                                                            |  |

| CoreFIM                   | Flexible configuration support using Arm* AMBA* 4 AXI4-Stream Physical Function/Virtual Function (PF/VF)<br>Demux/Mux and AFU Peripheral Fabric (APF) and Board Peripheral (BPF) Fabric Interconnects. |  |

| Physical Function/Virtual | 1 PF/3VF configuration is provided as an example but the architecture now supports full virtualization with the ability to expand to whatever the PCIe tile supports.                                  |  |

| Partial Reconfiguration   | 1 Partial Reconfiguration region supported in hardware and software                                                                                                                                    |  |

| Sample test PR AFUs       | Host exerciser modules provided to exercise interfaces. These modules are provided in both the flat and PR AFU examples.                                                                               |  |

| OneAPI                    | Yes                                                                                                                                                                                                    |  |

| Software Support          | OFS software stack with support for full virtualization.                                                                                                                                               |  |

### FPGA MANAGEMENT ENGINE (FME)

The FIM contains only one FME, regardless of the number of host interfaces to the FIM. The FME provides management features for the platform and controls reset and loading of the AFU into the partial reconfiguration region of the FPGA.

Each FME feature exposes its capability to host software drivers through a device feature header (DFH) register found at the beginning of its control status register (CSR) space. The FME CSR maps to physical function 0 (PF0) Base address register 0 (BAR0) so that software can access it through a single PCIe link. For more information about DFHs, refer to the [Device Feature Header (DFH) structure].

#### STREAMING DATAPATH

• The FIM implements an AXI4-Stream bus protocol for data transfer in the FIM. AXI4-Stream channels send data packets to and from the host channel IP without data abstraction. Memory-mapped I/O (MMIO) CSR accesses are routed to the ST2MM module which converts the AXI4-Stream to an AXI4 memory mapped protocol.

#### VIRTUALIZATION

• This design supports virtualization by making use of the virtualization functionality in the PCIe Hard IP and mapping packets to the appropriate physical or virtual function through a PF/VF multiplexer. This reference FIM supports 1 PF and 3 VFs as an example; however, you may extend your configuration to whatever the PCIe Hard IP can support or what your application requires.

### Accelerator Functional Unit (AFU)

- An AFU is an acceleration workload that interfaces to the FIM.

- The AFU boundary in this design comprises both static and partial reconfiguration (PR) regions. You can compile your design in one of the following ways:

- Your entire AFU resides in a partial reconfiguration region of the FPGA

- The AFU is part of the static region and is compiled a flat design

### Platform Interface Manager

- The PIM provides a way to abstract the AXI4-Stream interface to the AFU by providing a library of shims that convert the host channel native packet into other protocols such as

- CCI-P

- AXI4 memory-mapped

- Avalon<sup>®</sup> streaming (Avalon-ST)

- Avalon<sup>®</sup> memory-mapped (Avalon-MM).

- If you expose the raw AXI4-Stream interface of the FIM, workload developers also have the option to convert to a desired protocol using the PIM resources as well.

#### FIM Simulation

OFS provides a UVM environment for the FIM and a framework for new feature verification. UVM provides a modular, reusable, and scalable testbench structure by providing an API framework that can be deployed across multiple projects. The FIM testbench is UVM compliant and integrates third-party verification IPs from Synopsys that require license to use. Verification components include:

- FIM monitor to detect correct design behavior

- FIM assertions for signal level integrity testing

- Arm AMBA AXI4 scoreboards to check data integrity

- FIM coverage to collect functional data

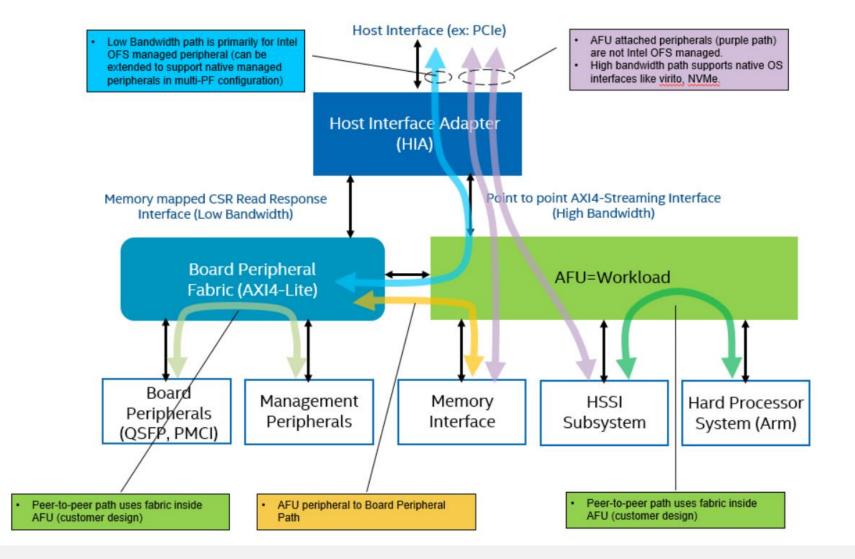

#### OFS Datapath

OFS provides distinct datapaths that simplifies the design and integration process for add or for removing interface modules:

- High Bandwidth datapath for AFU-attached high performance peripherals (HSSI, Memory, HPS, workload).

- Low Bandwidth datapath for OFS management and slow peripheral components (JTAG, I2C, SMBus).

- AFU Peripheral Fabric (APF) to Board Peripheral Fabric (BPF) path to communicate with interface control and status registers (CSRs) and board components.

- Peer-to-peer datapath between AFU components.

- **Peer-to-peer datapath** between BPF components.

Depending on your design goals, you can present peripherals to software as:

- OFS managed peripherals with a device feature header that is part of a device feature list.

- Native driver managed peripherals that are exposed through an independent physical function or virtual function.

#### OFS Datapath

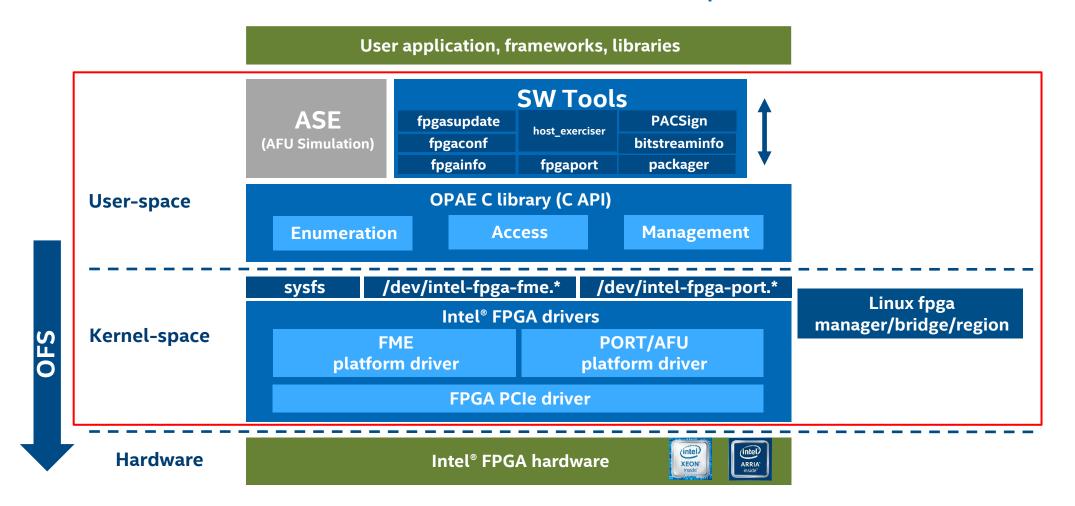

# OPAE-SDK

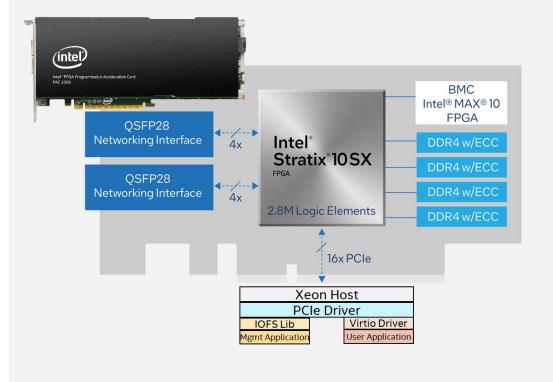

### OFS Software Stack Components

The OFS software stack (OPAE) is the lowest level of software that manages the FPGA card. Higher level software (OpenCL/oneAPI) can be built on top of OFS.

- Components—open source on Git

- libOPAE (user-space library)

- OPAE FPGA applications and tools (e.g. fpgainfo, fpgaconf, fpgasupdate, etc.)

- AFU Simulation environment (ASE)

- DFL Linux Kernel Driver

OPAE code is completely open source at: http://github.com/OFS/opae-sdk Open Programmable Acceleration Engine (OPAE) OPAE is a collection of APIs, libraries, and tools to provide FPGA abstraction

## Device Feature List (DFL)

#### OFS uses a DFL structure to describe FPGA contents to software

- The DFL is a Linked list of Device Feature Headers (DFH)

- DFL framework abstracts low layer hardware details and provides a unified interface to userspace

- DFL Linux Driver "walks" the DFL attaching/binding software to enumerate each FPGA feature

- DFL driver source code available at: github.com/OPAE/linux-dfl

- In the process of being upstreamed to kernel.org

### OPAE Tools Sample

| OPAE Tool     | Description                                                                                                                                                  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| fpgaconf      | Configures the FPGA with the accelerator function (AF). It also checks the AF for compatibility with the targeted FPGA and the FPGA Interface Manager (FIM). |  |

| fpgasupdate   | Implements a secure firmware for FPGA or BMC                                                                                                                 |  |

| fpgainfo      | Displays FPGA information derived from sysfs files                                                                                                           |  |

| rsu           | Allows the user to preform a remote system update (RSU) operation on a PAC device given its PCIe address                                                     |  |

| PACSign       | Inserts authentication markers into bitstreams targeted for the Intel FPGA PAC D5005                                                                         |  |

| bitstreaminfo | Displays authentication information contained with each provided FPGA bitstream binary file                                                                  |  |

| hssi          | Provides a means of interacting with the 10G HE-HSSI                                                                                                         |  |

| opae.io       | Provides user space access to PCIe devices via the vfio-pci driver                                                                                           |  |

...and many more

### fpgasupdate

- The fpgasupdate tool updates the Intel Max10 BMC image and firmware, root entry hash, and FPGA Static Region (SR) and user image (PR). The fpgasupdate will only accept images that have been formatted using PACsign. If a root entry hash has been programmed onto the board, then the image will also need to be signed using the correct keys.

- The Intel FPGA PAC ships with a factory and user programmed image for both the FIM and BMC FW and RTL on all cards.

- fpgasupdate [--log-level=<level>] file [bdf]

| args (optional) | Description                                                                                                                                                                                                                                                                                                                                       |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| log-level       | Specifies the log-level which is the level of information output to your command tool. The following seven levels are available: state, ioctl, debug, info, warning, error, critical. Settinglog-level=state provides the most verbose output. Settinglog-level=ioctl provides the second most information, and so on. The default level is info. |  |

| file            | Specifies the secure update firmware file to be programmed. This file may be to program a static region (SR), programmable region (PR), root entry hash, key cancellation, or other device-specific firmware.                                                                                                                                     |  |

| bdf             | The PCIe address of the PAC to program. bdf is of the form [ssss:]bb:dd:f, corresponding to PCIe segment, bus, d<br>function. The segment is optional. If you do not specify a segment, the segment defaults to 0000. If the system h<br>only one PAC you can omit the bdf and let fpgasupdate determine the address automatically.               |  |

fpgainfo [-h] [-S] [-B] [-D] [-F] [PCI\_ADDR] {errors,power,temp,fme,port,bmc,mac,phy,security}

| Command  | args (optional)           | Description                                                                                                                                                                  |

|----------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | help, -h                  | Prints help information and exits.                                                                                                                                           |

|          | version, -v               | Prints version information and exits.                                                                                                                                        |

|          | segment, -S               | PCIe segment number of resource.                                                                                                                                             |

|          | bus, -B                   | PCIe bus number of resource                                                                                                                                                  |

|          | device, -D                | PCIe device number of resource.                                                                                                                                              |

|          | function, -F              | PCIe function number of resource.                                                                                                                                            |

| errors   | {fme, port, all}clear, -c | First agument to the errors command specifies the resource type to display in human readable format. The second optional argument clears errors for the given FPGA resource. |

| power    |                           | Provides total power in watts that the FPGA hardware consumes                                                                                                                |

| temp     |                           | Provides FPGA temperature values in degrees Celsius                                                                                                                          |

| port     |                           | Provides information about the port                                                                                                                                          |

| fme      |                           | Provides information about the FME                                                                                                                                           |

| bmc      |                           | Provides BMC sensors information                                                                                                                                             |

| mac      |                           | Provides information about MAC ROM connected to FPGA                                                                                                                         |

| security |                           | Provides information about the security keys, hashes, and flash count, if available.                                                                                         |

- Performed remote system update operation on a device, given its PCIe address. A rsu operation sends an instruction to the device to trigger a power cycle of the card only. This will force reconfiguration from flash for either the BMC or FPGA.

- The Intel FPGA PAC contains a region of flash the user may store their FIM image. After an image has been programmed with fpgasupdate the user may choose to perform rsu to update the image on the device.

- bash session

- rsu [-h] [-d] {bmc,bmcimg,retimer,sdm,fpgadefault} [PCIE\_ADDR]

- Opae.io is an interactive Python environment which provides user space access to PCIe devices via vfiopci driver.

- The main features of opae.io is its build-in Python command interpreter that provide a means to access Configuration and Status Registers (CSRs) that reside on the PCIe device

- Opae.io has 2 operating modes

- Command line

- Interactive mode

# Opae.io example

- Opae.io ls [-v, --viddid VID:DID]

- List each accelerator device along with the PCIe address, PCIe vendor/device ID, brief description and the driver to which the currently is bound

- Opae.io init [-d PCI\_ADDR USER:[GROUP]]

- Unbinds the specific device from its current driver and binds it to vfio-pci

- Opae.io release [-d PCI\_ADDR]

- Release the device form vfio-pci

- Opae.op walk [-d PCI\_ADDR] [-r REGION] [OFFSET] [-u, --show-uuid]

- Traverses and display the Device Features List of the given region

- Opae.io peek [-d PCI\_ADDR] [-r REGION] OFFSET

- Options reads and displays a CSR value

- Opae.io poke [-d PCI\_ADDR [-r REGION] OFFSET VALUE

- Writes a given value to a CSR

# OFS Development Guide

### Stratix 10 Architecture

### Pre-requisites

OFS is an advanced application of FPGA technology. This guide assumes you have the following FPGA logic design-related knowledge and skills:

- FPGA compilation flows using Intel<sup>®</sup> Quartus<sup>®</sup> Prime Pro Edition design flow.

- Static Timing closure, including familiarity with the Timing Analyzer tool in Intel<sup>®</sup> Quartus<sup>®</sup> Prime Pro Edition, applying timing constraints, Synopsys\* Design Constraints (.sdc) language and Tcl scripting, and design methods to close on timing critical paths.

- RTL and coding practices for FPGA implementation.

- RTL simulation tools.

- Intel<sup>®</sup> Quartus<sup>®</sup> Prime Pro Edition Signal Tap Logic Analyzer tool software.

## Development Environment

| ltem                                | Version                                           |  |

|-------------------------------------|---------------------------------------------------|--|

| Intel Quartus Prime Pro             | Intel Quartus Prime Pro 22.3 (with license patch) |  |

| Target D5005 Sever Operating System | RHEL 8.2                                          |  |

| OPAE SDK                            | <u>2.3.0-1</u>                                    |  |

| Linux DFL                           | <u>ofs-2022.3-2</u>                               |  |

| Python                              | 3.7.7                                             |  |

| cmake                               | 3.11.4                                            |  |

| GCC                                 | 7.2.0                                             |  |

| perl                                | 5.8.8                                             |  |

# Reference Board FIM

Host interface

•PCle Gen3 x 16

- •2 QSFP28 cages

- •Current FIM supports 1 x 10 GbE, other interfaces can be created

•External Memory

- •2 or 4 channels of DDR4-2400 to RDIMM modules

- •RDIMM modules = 8GB organized as 1 Gb X 72

- Board Management

- •SPI interface

- •FPGA configuration

FCCM 2023

# FIM FPGA Resource Usage

| Summary                         | FPGA Resource Utilization          |

|---------------------------------|------------------------------------|

| Logic utilization (in ALMs)     | 124,092 / 933,120 ( 13 % )         |

| Total dedicated logic registers | 282822                             |

| Total pins                      | 630/912(69%)                       |

| Total block memory bits         | 3,425,120 / 240,046,080 ( 1<br>% ) |

| Total RAM Blocks                | 661 / 11,721 ( 6 % )               |

| Total DSP Blocks                | 0 / 5,760 ( 0 % )                  |

| Total eSRAMs                    | 0/75(0%)                           |

| Total HSSI P-Tiles              | 17 / 48 ( 35 % )                   |

| Total HSSI E-Tile Channels      | 17 / 48 ( 35 % )                   |

| Total HSSI HPS                  | 0/1(0%)                            |

| Total HSSI EHIPs                | 0/2(0%)                            |

| Total PLLs                      | 36 / 104 ( 35 % )                  |

## OFS Contents

| Eval Script | Contains scripts for evaluation of OFS for D5005 including compiling FIM/AFU from source, unit level test.<br>Also includes resources to report and setup D5005 development environment                                                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ipss        | Contains the code and supporting files that define or set up the IP subsystems (HSSI, PCIe, memory, PMCI, SPI, etc) contained in the D5005 FPGA Interface Manager (FIM).                                                                                                                                                        |

| License     | License file for the Low Latency 10Gbps Ethernet MAC (6AF7 0119) IP core.                                                                                                                                                                                                                                                       |

| ofs-common  | This directory contains resources that may be used across the board-specific repositories. This directory is referenced via a link within each of the FPGA-specific repositories.                                                                                                                                               |

| Sim         | Contains the testbenches and supporting code for all the unit test simulations.<br>Bus Functional Model code is contained here.<br>Scripts are included for automating a myriad of tasks.<br>All of the individual unit tests and their supporting code is also located here.                                                   |

| Src         | SystemVerilog source and script files<br>Contains all of the structural and behavioral code for the FIM.<br>Scripts for generating the AXI buses for module interconnect.<br>Top-level RTL for synthesis is located in this directory.<br>Accelerated Functional Unit (AFU) infrastructure code is contained in this directory. |

| Syn         | This directory contains all of the scripts, settings, and setup files for running synthesis on the FIM.                                                                                                                                                                                                                         |

# Linux OS package requirement

- RHEL 8.2 Library needed

- sudo dnf install libnsl sudo dnf install ncurses-compat-libs

- sudo ln -s /usr/bin/python3 /usr/bin/python

# **OFS Installation**

- Install Quartus Prime Pro 22.3 Linux and setup environment

- Clone the github `ofs-d5005` repository

- mkdir OFS\_fim\_build\_root

- cd OFS\_fim\_build\_root

- export OFS\_BUILD\_ROOT=\$PWD

- git clone --recurse-submodules https://github.com/OFS/ofs-d5005.git

- cd ofs-d5005

- git checkout tags/ofs-d5005-1.0.1

- Install Quartus Patch

- cd license

- chmod +x quartus-0.0-0.01OFS-linux.run

- sudo ./quartus-0.0-0.01OFS-linux.run

- Test installation by building the provided FIM

# Setting up the environment

- cd \$OFS\_BUILD\_ROOT/ofs-d5005

- export OFS\_ROOTDIR=\$PWD

- OFS\_ROOTDIR is the directory where you cloned the repo, e.g. /home/MyProject/ofs-d5005 \*

- export WORKDIR=\$OFS\_ROOTDIR

- export VERDIR=\$OFS\_ROOTDIR/verification

- export QUARTUS\_HOME=\$QUARTUS\_ROOTDIR

- QUARTUS\_ROOTDIR is your Quartus installation directory, e.g. \$QUARTUS\_ROOTDIR/bin contains Quartus executuable\*

- export QUARTUS\_INSTALL\_DIR=\$QUARTUS\_ROOTDIR

- export IMPORT\_IP\_ROOTDIR=\$QUARTUS\_ROOTDIR/../ip

- export IP\_ROOTDIR=\$QUARTUS\_ROOTDIR/../ip

- export OPAE\_SDK\_REPO\_BRANCH=release/2.3.0

# Compilation

- ofs-common/scripts/common/syn/build\_top.sh [-p] target\_configuration work\_dir

- Usage: ofs-common/scripts/common/syn/build\_top.sh [-k] [-p] []

- target\_configuration Specifies the project

For example: d5005

- work\_dir

- Work Directory for this build in the form a directory name. It is created in the <local repo directory>/ofs-d5005/<work\_dir> NOTE:

- The directory name must start with "work". If the work directory exists, then the script stops and asks if you want to overwrite the directory.

- Example

- ofs-common/scripts/common/syn/build\_top.sh d5005 work\_d5005

- work directory as a name will be created in <local repo directory>/ofs-d5005/work\_d5005

- The obmission of <work\_dir> results in a default work directory (<local repo directory>/ofs-d5005/work)

- compile reports and artifacts (.rpt, .sof, etc) are stored in <work\_dir>/syn/syn\_top/output\_files

- There is a log file created in ofs-d5005 directory.

| File                     | Description                                                                                                                                                                                                                                                      |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| d5005.sof                | This is the Quartus generated programming file created by Quartus synthesis and place and route. This file can be used to programming the FPGA using a JTAG programmer. This file is used as the source file for the binary files used to program the FPGA flash |

| d5005.bin                | This is an intermediate raw binary image of the FPGA                                                                                                                                                                                                             |

| d5005_page1.bin          | This is the binary file created from input file, d5005.sof. This file is used as the input file to the PACSign utility to generate "d5005_page1_unsigned.bin" binary image file.                                                                                 |

| d5005_page1_unsigned.bin | This is the unsigned PACSign output which can be programmed into the FPGA flash of an unsigned D5005 using the OPAE SDK utility "fpgasupdate"                                                                                                                    |

| mfg_d5005_reversed.bin   | A special programming file for a third party programming device used in board manufacturing. This file is typically not used.                                                                                                                                    |

# Enable PR

- cd \$OFS\_BUILD\_ROOT

- git clone https://github.com/OPAE/ofs-platform-afu-bbb

- cd ofs-platform-afu-bbb

- export OFS\_PLATFORM\_AFU\_BBB=\$PWD

- cd \$OFS\_ROOTDIR

- syn/common/scripts/generate\_pr\_release.sh -t work\_d5005/build\_tree d5005 work\_d5005

# PR Build Tree

- Bin

- Afu\_synth

- Build\_env\_config

- Run.sh

- Update\_pim

- Hw

- Blue\_bbits

- D5005\_page1\_unsigned.bin

- D5005.sof

- Lib

- Build

- Fme-ifc-id.txt

- Fme-platform-class.txt

- platform

# **Unit Level Simulation**

- Key components provided

- HSSI

- PCle

- External Memory

- FIM management

- Simulation Requirement

- Python

- Quartus

- VCS

# **Running simulation**

- Compiling all IP

- cd \$OFS\_ROOTDIR/ofs-common/scripts/common/sim

- sh gen\_sim\_files.sh d5005

- IP Simulation filelist

- \$OFS\_ROOTDIR/sim/scripts/ip\_flist.f

- RTL file list for unit\_test

- \$OFS\_ROOTDIR/sim/scripts/rtl\_comb.f

- IPs generated

- \$OFS\_ROOTDIR/sim/scripts/qip\_gen

- Running the simulation

- \$OFS\_ROOTDIR/sim/unit\_test/<Unit Test Name>/scripts

- sh run\_sim.sh VCS=1

# OFS with SignalTap

- Perform a full compile using the script build\_top.sh.

- Once the compile completes open the Quartus GUI using the FIM project. The Quartus project is named d5005 and is located in the work directory syn/syn\_top/d5005.qpf. Once the project is loaded, go to Tools > Signal Tap Logic Analyzer to bring up the Signal Tap GUI.

- Add the signal needed for debug

# AFU Developer Guide

## OFS FIM

- OFS provides a build script with the following FPGA image creation options:

- Flat compile, which combines the FIM and AFU into one FPGA image loaded into the entire FPGA device as static image

- PR (Partial Reconfiguration) compile that creates an FPGA image consisting of the FIM that is loaded into the static region of the FPGA and a default AFU that is loaded into dynamic region.

- Build scripts included with OFS are verified to run in bash shell

# Flat Compile

# Hello FIM example (Top Level design)

If you intend to add a new module to the FIM area, then you will need to inform the host software of the new module. The FIM exposes its functionalities to host software through a set of CSR registers that are mapped to an MMIO region (Memory Mapped IO). This set of CSR registers and their operation is described in FIM MMIO Regions.

Step to add simple DFH register

- 1. Review current design documentation: OFS Tech Ref MMIO Regions

- 2. Understand FME and Port regions, DFH walking, DFH register structure

- 3. Run unit level simulations and review output: i. sim/unit\_test/dfh\_walker

- 4. Note DFH link list order, see DFH Walker Unit Level Simulation Output

- 5. Make code changes to top level FIM file to instantiate new DFH register

- 6. The DFH registers follow a link list. This example inserts the hello\_fim DFH register after the EMIF DFH register, so the emif\_csr.sv parameters are updated to insert the hello\_fim DFH register as next register in the link list.

- 7. Create the new hello\_fim SystemVerilog files.

- 8. Update and run the dfh\_walker unit simulation files

- 9. Update synthesis files to include the new hello\_fim source files

- 10. Build and test the new FIM

# **OFS Top Level**

### src/top/iofs\_top.sv

| Address              | Size (Byte) | Feature                           | Master |

|----------------------|-------------|-----------------------------------|--------|

| 0x00000 –<br>0x0FFFF | 64K         | FME (FME,<br>Error, etc)          | Yes    |

| 0x10000 –<br>0x1FFFF | 64K         | PMCI Proxy<br>(SPI<br>Controller) | Yes    |

| 0x20000 –<br>0x2FFFF | 64K         | PCIe CSR                          |        |

| 0x30000 –<br>0x3FFFF | 64K         | HSSI CSR                          |        |

| 0x40000 –<br>0x4FFFF | 64K         | EMIF CSR                          |        |

| 0x50000 –<br>0x5FFFF | 64K         | Reserved                          |        |

| 0x60000 –<br>0x6FFFF | 64K         | Reserved                          |        |

| 0x70000 –<br>0x7FFFF | 64К         | Reserved                          |        |

#### fme\_top fme\_top

| _top | (              |                 |    |    |

|------|----------------|-----------------|----|----|

|      | .clk           | (clk_1x         |    | ), |

|      | .rst_n         | (rst_n_d_1x     | ), |    |

|      | .pwr_good_n    | (ninit_done     |    | ), |

|      | .i_pcie_error  | ('0             |    | ), |

|      | .axi_lite_m_if | (bpf_fme_mst_if |    | ). |

|      | .axi_lite_s_if | (bpf_fme_slv_if |    | )  |

|      | );             | (               |    |    |

|      |                |                 |    |    |

#### `ifdef INCLUDE\_HELLO\_FIM

hello\_fim\_top hello\_fim\_top ( .clk (clk\_1x),

.rst\_n .csr\_lite\_if (rst\_n\_d\_1x), (bpf\_rsv\_5\_slv\_if)

#### );

`endif

// Reserved address response

`ifndef INCLUDE\_HELLO\_FIM

bpf\_dummy\_slv

bpf\_rsv\_5\_slv (

.clk (clk\_1x),

.dummy\_slv\_if (bpf\_rsv\_5\_slv\_if)

);

`endif

# EMIF CSR (ipss/mem/emif\_csr.sv)

The Hello\_FIM DFH is inserted in the DFH link list after the EMIF CSR DFH and before the FME\_PR DFH. The file ipss/d5005/emif/emif\_csr.sv contains a parameter defining the next address for the next DFH in in the link list chain. You will change the next address offset to be 0x10000 so the reserved BPF AXI lite link connected to the Hello\_FIM DFH register is next in the DFH link list.

```

module emif_csr #(

parameter NUM_LOCAL_MEM_BANKS = 1,

parameter END_OF_LIST = 1'b0,

`ifndef INCLUDE_HELLO_FIM

parameter NEXT_DFH_OFFSET = 24'h05_0000

`else

parameter NEXT_DFH_OFFSET = 24'h01_0000//New for Hello_FIM, next offset now at 0x50000

`endif

```

# Hello FIM TOP (src/hello\_fim/hello\_fim\_top.sv)

- Create hello\_fim\_top.sv, and store it in src/hello\_fim directory.

- The main purpose of this RTL is to convert AXI4-Lite interface to a simple interface to interface with the registers in hello\_fim\_com.sv.

- This register sets the DFH feature ID to 0xfff which is undefined.

- For test purposes, using an undefined feature ID will result in no driver being used.

- Normally, a defined feature ID will be used to associate a specific driver with the FPGA module.

```

module hello_fim_top #(

parameter ADDR_WIDTH = 12,

parameter DATA_WIDTH = 64,

parameter bit [11:0] FEAT_ID = 12'hfff,

parameter bit [3:0] FEAT_VER = 4'h0,

parameter bit [23:0] NEXT_DFH_OFFSET = 24'h04_0000,

parameter bit END_OF_LIST = 1'b0

)(

input logic clk,

input logic rst_n,

```

# Hello FIM COM (src/hello\_fim/hello\_fim\_com.sv)

Create hello\_fim\_com.sv, and store it in src/hello\_fim directory. This is the simple RTL to implement the Hello FIM registers. You may use this set of registers as the basis for your custom implementation.

```

module hello_fim_com #(

parameter bit [11:0] FEAT_ID = 12'h001,

parameter bit [3:0] FEAT_VER = 4'h1,

parameter bit [23:0] NEXT_DFH_OFFSET = 24'h1000,

parameter bit END_OF_LIST = 1'b0

) (

input clk,

input rst_n,

input [63:0] writedata,

input read,

input write,

input [3:0] byteenable,

output reg [63:0] readdata,

output reg readdatavalid,

input [5:0] address

);

```

# Update setting fiile

- Edit syn/syn\_top/d5005.qsf

- set\_global\_assignment -name VERILOG\_MACRO INCLUDE\_HELLO\_FIM

- set\_global\_assignment -name SOURCE\_TCL\_SCRIPT\_FILE ../../syn/setup/hello\_fim\_design\_files.tcl

# Build hello\_fim example

- Execute command

- cd \$OFS\_ROOTDIR

- ofs-common/scripts/common/syn/build\_top.sh d5005 work\_d5005\_hello\_fim

- Updating the board

- sudo fpgasupdate d5005\_page1\_unsigned.bin <D5005 PCIe B:D.F>

- sudo rsu bmcimg <D5005 PCIe B:D.F>

# Running Hello World

sudo opae.io init -d 0000:12:00.0 \$USER

##Output opae.io 0.2.3 Unbinding (0x8086,0xbcce) at 0000:12:00.0 from dfl-pci Binding (0x8086,0xbcce) at 0000:12:00.0 to vfio-pci iommu group for (0x8086,0xbcce) at 0000:12:00.0 is 35 Assigning /dev/vfio/35 to \$USER opae.io ls ## Output opae.io 0.2.3 [0000:12:00.0] (0x8086, 0xbcce) Intel D5005 ADP (Driver: vfio-pci) \$ opae.io -d 0000:12:00.0 -r 0 peek 0x50000 opae.io 0.2.3 0x3000000400000fff \$ opae.io -d 0000:12:00.0 -r 0 peek 0x50030 opae.io 0.2.3 0x0 \$ opae.io -d 0000:12:00.0 -r 0 peek 0x50038 opae.io 0.2.3 0x6626070150000034 sudo opae.io release -d 0000:12:00.0 ## Output opae.io 0.2.3 Releasing (0x8086,0xbcce) at 0000:12:00.0 from vfio-pci Rebinding (0x8086,0xbcce) at 0000:12:00.0 to dfl-pci \$ sudo opae.io ls opae.io 0.2.3 [0000:12:00.0] (0x8086, 0xbcce) Intel D5005 ADP (Driver: dfl-pci) opae.io walk -d 0000:12:00.0

## Output

opae.io 0.2.3

offset: 0x0000, value: 0x4000000010000000

dfh: id = 0x0, rev = 0x0, next = 0x1000, eol = 0x0, reserved = 0x0, feature\_type = 0x4 offset: 0x1000, value: 0x300000020000001

dfh: id = 0x1, rev = 0x0, next = 0x2000, eol = 0x0, reserved = 0x0, feature\_type = 0x3 offset: 0x3000, value: 0x300000010000007

dfh: id = 0x7, rev = 0x0, next = 0x1000, eol = 0x0, reserved = 0x0, feature\_type = 0x3 offset: 0x4000, value: 0x30000000c0001004

dfh: id = 0x4, rev = 0x1, next = 0xc000, eol = 0x0, reserved = 0x0, feature\_type = 0x3 offset: 0x10000, value: 0x30000010000000e

dfh: id = 0xe, rev = 0x0, next = 0x10000, eol = 0x0, reserved = 0x0, feature\_type = 0x3 offset: 0x20000, value: 0x3000000100000020

dfh: id = 0x20, rev = 0x0, next = 0x10000, eol = 0x0, reserved = 0x0, feature\_type = 0x3 offset: 0x30000, value: 0x3000001000100f

dfh: id = 0xf, rev = 0x1, next = 0x10000, eol = 0x0, reserved = 0x0, feature\_type = 0x3 offset: 0x40000, value: 0x300000100000009

dfh: id = 0x9, rev = 0x0, next = 0x10000, eol = 0x0, reserved = 0x0, feature\_type = 0x3 offset: 0x50000, value: 0x3000000400000fff

dfh: id = 0xfff, rev = 0x0, next = 0x40000, eol = 0x0, reserved = 0x0, feature\_type = 0x3 offset: 0x90000, value: 0x300000010001005

dfh: id = 0x5, rev = 0x1, next = 0x1000, eol = 0x0, reserved = 0x0, feature\_type = 0x3 offset: 0x91000, value: 0x400000010001001

dfh: id = 0x1, rev = 0x1, next = 0x1000, eol = 0x0, reserved = 0x0, feature\_type = 0x4 offset: 0x92000, value: 0x300000010000014

dfh: id = 0x14, rev = 0x0, next = 0x1000, eol = 0x0, reserved = 0x0, feature\_type = 0x3 offset: 0x93000, value: 0x3000000000002013

dfh: id = 0x13, rev = 0x2, next = 0xd000, eol = 0x0, reserved = 0x0, feature\_type = 0x3 offset: 0xa0000, value: 0x3000010000002010

dfh: id = 0x10, rev = 0x2, next = 0x0, eol = 0x1, reserved = 0x0, feature\_type = 0x3

# PR compile

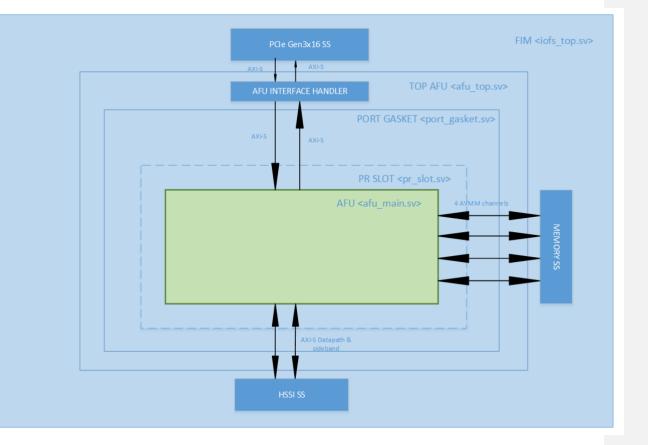

# OFS FIM for PR Compile

- AXI Streaming (AXI-S) interface to Host via PCIe Gen3xx16

- Avalon Memory-Mapped Channels (4) to the DDR4 EMIF interface

- AXI Streaming (AXI-S) interface to the HSSI 10G Ethernet

# Platform Interface Manager (PIM)

- PIM is a transformation layer between an AFU and raw FIM device interface.

- Standard AFU-side SystemVerilog interfaces, both AXI and Avalon memory mapped and streaming.

- PIM-provided modules that transform FIM interfaces to PIM interfaces. Transformations may be simple, such as mapping a FIM AXI-MM interface to the PIM's AXI-MM. Transformations may also be complex, such as mapping a PCIe TLP stream to AXI-MM, adding a clock crossing and sorting read responses.

- A top-level module and interface bundle with consistent naming across all platforms, promoting AFU portability.

- Ofs-platform-afu-bbb repository contains the PIM files and example AFU.

- git clone <a href="https://github.com/OFS/ofs-platform-afu-bbb.git">https://github.com/OFS/ofs-platform-afu-bbb.git</a>

# Top module

- If using PIM

- ofs\_plat\_afu.sv

- ex) <u>https://github.com/OFS/examples-</u> afu/blob/main/tutorial/afu\_types/01\_pim\_ifc/hello\_world/hw/rtl/avalon/ofs\_plat\_afu.sv

- If not using PIM

- afu\_main.sv

- ex) <u>https://github.com/OFS/examples-</u> <u>afu/blob/main/tutorial/afu\_types/03\_afu\_main/hello\_world/hw/rtl/afu\_main.sv</u>

- Need to handle AXI streaming I/F which includes PCIE TLP packets by developer themselves

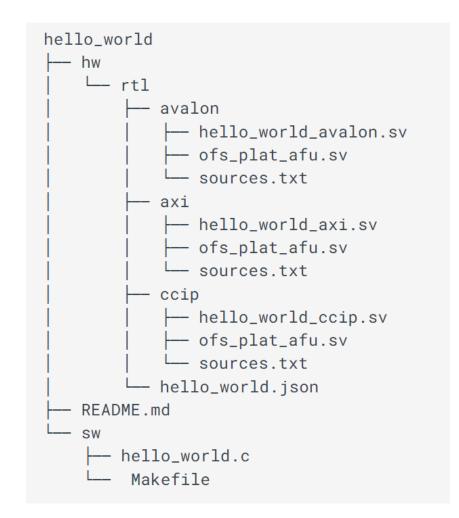

# Example AFU (hello\_world)

- Compiling and executing PIM-based hello\_world AFU

- hw directory contains the RTL to implement the hardware functionality using CCIP, Avalon and AXI interface

- Sw directory contains source code of the host application that communicates with the AFU hardware

- git clone https://github.com/OFS/examplesafu.git

#### Compiling hello\_world sample AFU

- Environment setup

- export FPGA\_BBB\_CCI\_SRC=\$OFS\_BUILD\_ROOT/examples-afu

- export OPAE\_PLATFORM\_ROOT=\$OFS\_ROOTDIR/work\_d5005/build\_tree

- Execute

- ofs-common/scripts/common/syn/generate\_pr\_release.sh -t work\_d5005/build\_tree d5005 work\_d5005

- afu\_synth\_setup -s \$FPGA\_BBB\_CCI\_SRC/tutorial/afu\_types/01\_pim\_ifc/hello\_world/hw/rtl/axi/sources.txt hello\_world\_synth

- cd hello\_world\_synth

- \${OPAE\_PLATFORM\_ROOT}/bin/afu\_synth

- "hello\_world.gbs" bitstream will be created

### Running the AFU

- Update PR image

- sudo fpgasupdate hello\_world.gbs 3b:00.0

- Create virtual function (VFs) and bond VFs to VFIO Driver

- sudo pci\_device 3b:00.0 vf 3

- sudo opae.io init -d 0000:3b:00.1 <Your username>

- sudo opae.io init -d 0000:3b:00.2 <Your username>

- sudo opae.io init -d 0000:3b:00.3 <Your username>

- Host Application

- cd \$FPGA\_BBB\_CCI\_SRC/tutorial/afu\_types/01\_pim\_ifc/hello\_world/sw/

- make

- ./hello\_world Hello world TLP!

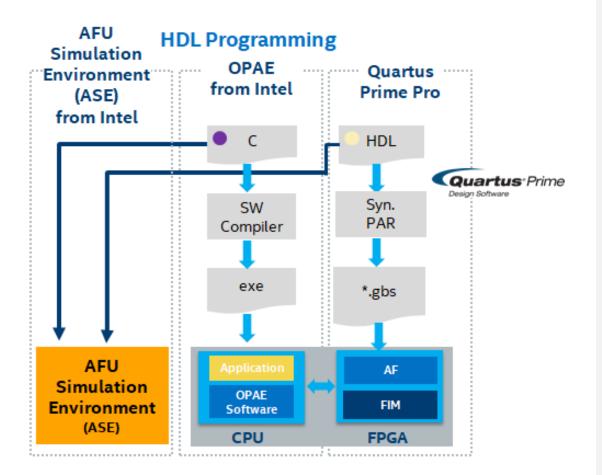

## AFU Simulation Environment (ASE)

- ASE is a hardware/software co-simulation environment for AFU

- ASE uses the simulator Direct Programming Interface (DPI) to provide HW/SW connectivity.

- The PCIe connection is emulated with transactional model

#### ASE Operation

- Attempts to replicate the transactions that will be seen in real system.

- Provides a memory model to AFU, so illegal memory accesses can be identified early.

- Not a cache simulator.

- Does not guarantee synthesizability or timing closure.

- Does not model system latency.

- No administrator privileges are needed to run ASE. All code is user level.

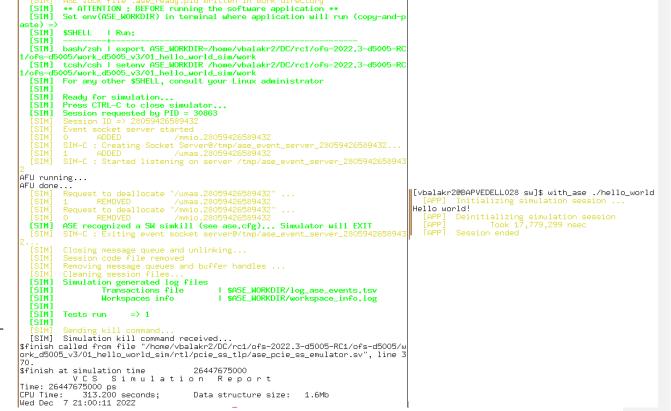

### Running ASE

- Set the environment variables

- Preparing hello\_world AFU for SIM

- afu\_sim\_setup -s \$FPGA\_BBB\_CCI\_SRC/tutorial/afu\_types/01\_pim\_ifc/hello\_ world/hw/rtl/axi/sources.txt -t VCS hello\_world\_sim

- Build and execute the AFU RTL simulator

- cd \$OFS\_ROOTDIR/work\_d5005/hello\_world\_sim

- make

- make sim

- Open second shell for host software

- export ASE\_WORKDIR=\$OFS\_ROOTDIR/work\_d5005/hello\_world\_ sim/work

- cd \$FPGA\_BBB\_CCI\_SRC/examplesafu/tutorial/afu\_types/01\_pim\_ifc/hello\_world/sw

- make

- with\_ase ./hello\_world

# Summary

### Why is OFS?

- Use Standard Interfaces and Application Programming Interfaces (APIs) to accelerate workload development and enable code reuse

- Port existing workloads to the Acceleration Functional Unit (AFU) Region and proliferate across OFS-based platforms for FPGA-based acceleration or CPU offload

- Utilize a growing ecosystem of OFS-enabled boards and workloads provided by Intel and third parties

- Deploy Bare Metal, Virtualized, or Containerized applications with data center class management for NFV, SmartNIC, VRAN, FSI, and more

- Build Application Specific FPGA Interface Managers (FIMs) from the provided reference FIMs using a modular, 'take and tailor' approach

- Leverage Open-Sourced and Upstreamed Software Code delivered via Git Repositories with native support from leading software vendors

- Reuse drivers for new cards & gens

- Get bug fixes from community

- Code reviewed by community

- Influence kernel development

- Avoid 3<sup>rd</sup> party impl. conflicts

- Enable more developers

### Check out OFS: <u>https://github.com/OFS</u>!

#### **OFS BASE FIM**

- FIM COMMON

<u>https://github.com/OFS/ofs-fim-common</u>

- OFS-D5005 (Intel Stratix 10) <u>https://github.com/OFS/ofs-d5005</u>

#### **Drivers and SW Tools**

- LINUX-DFL <u>https://github.com/OFS/linux-dfl</u>

- OPAE-SDK

https://github.com/OFS/opae-sdk

#### **Validation Framework**

OPAE-SIM <u>https://github.com/OFS</u> <u>/opae-sim</u>

| Term                                                              | Acronym                     | Description                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPGA Interface Manger                                             | FIM                         | FIMs provide platform management, functionality, clocks, resets, and standard interfaces to the host and AFU. Reference FIMs are provided as working examples to help users develop their own custom platforms. Users can 'take and tailor' the reference FIMs.                                                                                                           |

| Acceleration Functional Unit<br>Region                            | AFU                         | This region is the designated area for custom workload development, containing both static and dynamic regions.                                                                                                                                                                                                                                                           |

| Partial Reconfiguration Region                                    | PR                          | Region in the AFU for dynamically programming part or all of the workload.                                                                                                                                                                                                                                                                                                |

| FPGA Management Engine                                            | FME                         | Contains FPGA management CSRs and logic for global control of the device.                                                                                                                                                                                                                                                                                                 |

| Hard Processor System                                             | HPS                         | The HPS in the Agilex architecture has a quad core ARM Cortex A-53 MPCore and integrates a wide set of peripherals to reduce board size and increase performance                                                                                                                                                                                                          |

| Board Management Controller                                       | ВМС                         | Controls, monitors, and grants access to board features providing Root of Trust using a MAX 10 FPGA. The Agilex architecture includes an enhanced BMC architecture.                                                                                                                                                                                                       |

| Subsystems                                                        |                             | Memory, PCIe, and HSSI are built as modular subsystem to make them easier to modify.                                                                                                                                                                                                                                                                                      |

| Interconnect Fabrics                                              |                             | Route packets from PCIe subsystem to respective PF/VF functions.                                                                                                                                                                                                                                                                                                          |

| Host Exerciser Modules                                            | HE-LBK, HE-<br>MEM, HE-HSSI | Host exercisers do full memory, PCIe, or ethernet loopbacks to demonstrate external interface capabilities. Host exercisers are evaluation tools and not meant to included in production designs.                                                                                                                                                                         |

| AXI-Lite Interface                                                |                             | AXI is an industry-standard interface protocol. AXI provides a standardized IP protocol compatible with ARM and ARM partners.                                                                                                                                                                                                                                             |

| Universal Verification<br>Methodology Support                     | UVM                         | This industry standard verification environment is provided for the FIM & AFU.                                                                                                                                                                                                                                                                                            |

| Open Programmable Acceleration<br>Engine Software Development Kit | OPAE SDK                    | A collection of libraries and tools to facilitate the development of software applications and accelerators using OPAE.                                                                                                                                                                                                                                                   |

| Platform Interface Manager                                        | PIM                         | An interface manager that comprises two components: a configurable platform specific interface for board developers and a collection of shims that AFU developers can use to handle clock crossing, response sorting, buffering and different protocols.                                                                                                                  |

| Remote System Update                                              | RSU                         | A remote system update operation sends an instruction to the device that triggers a power cycle of the card only, forcing reconfiguration                                                                                                                                                                                                                                 |

| Device Feature List                                               | DFL                         | A main component of the software infrastructure for OFS. The DFL driver provides support for FPGA devices that are designed to support the Device Feature List. The DFL, which is implemented in RTL, consists of a self-describing data structure in PCI BAR space that allows the DFL driver to automatically load the drivers required for a given FPGA configuration. |

| AFU Simulation Environment                                        | ASE                         | A hardware/software co-simulation environment provided for the AFU as part of OPAE.                                                                                                                                                                                                                                                                                       |

- Ofs.github.io

- <u>https://github.com/OFS/examples-afu/</u>

- <u>https://github.com/OFS/ofs-platform-afu-bbb</u>