## Automatic High-Level Hardware Checkpoint Selection for Reconfigurable Systems

Alban Bourge, Olivier Muller and Frederic Rousseau

Univ. Grenoble Alpes TIMA Lab. Grenoble, France F-38031

05/05/2015

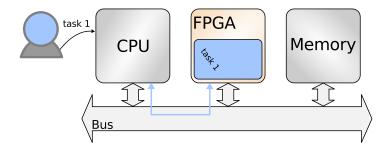

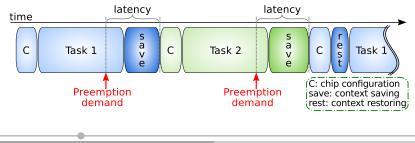

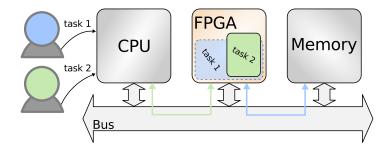

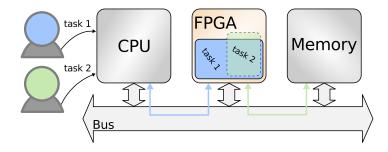

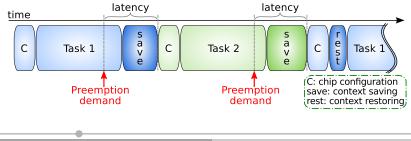

### Hardware context switch

1/4

### Hardware context switch

1/4

### Hardware context switch

1/4

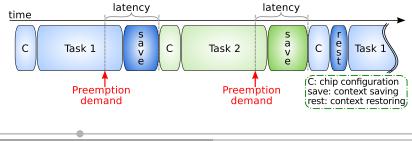

### Contributions

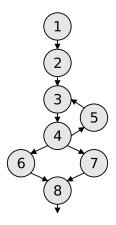

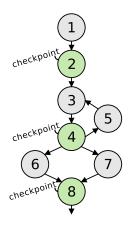

Algorithm with 2 inputs:

- ${\scriptstyle \bullet}\,$  FSM of the HW task

- Latency

### Contributions

Algorithm with 2 inputs:

- FSM of the HW task

- Latency

- $\Rightarrow$  set of checkpoints Circuit produced:

- Minimized area overhead

- Reduced memory footprint

- Respect preemption latency

Algorithm implemented in an HLS tool

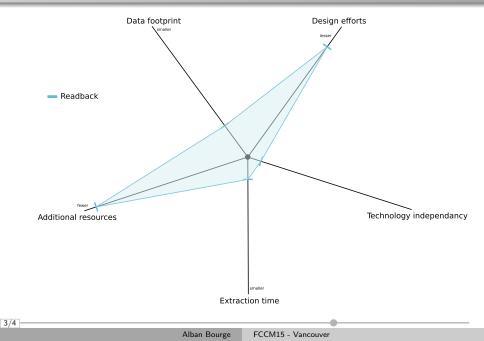

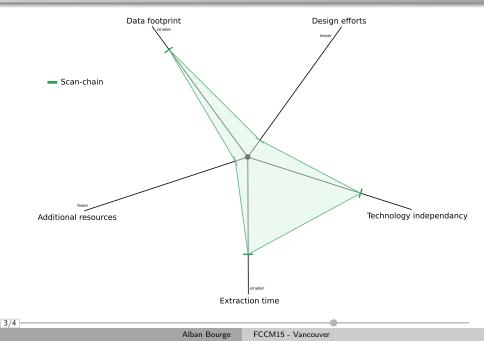

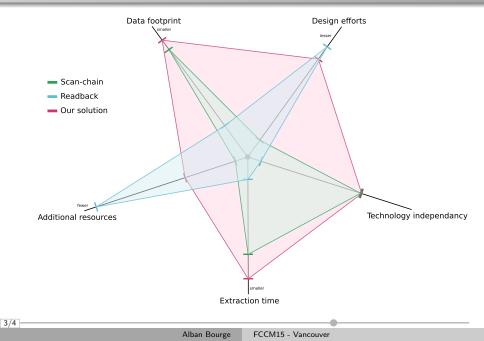

# Comparison

# Comparison

# Comparison

Further presentation of contributions:

- results !

85% less memory elements to save

52% HW overhead reduction

- more details about the method and implementation

- come and see our open source HLS tool AUGH and its plugin CP3