The 23<sup>rd</sup> IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM 2015) May 4, 2015

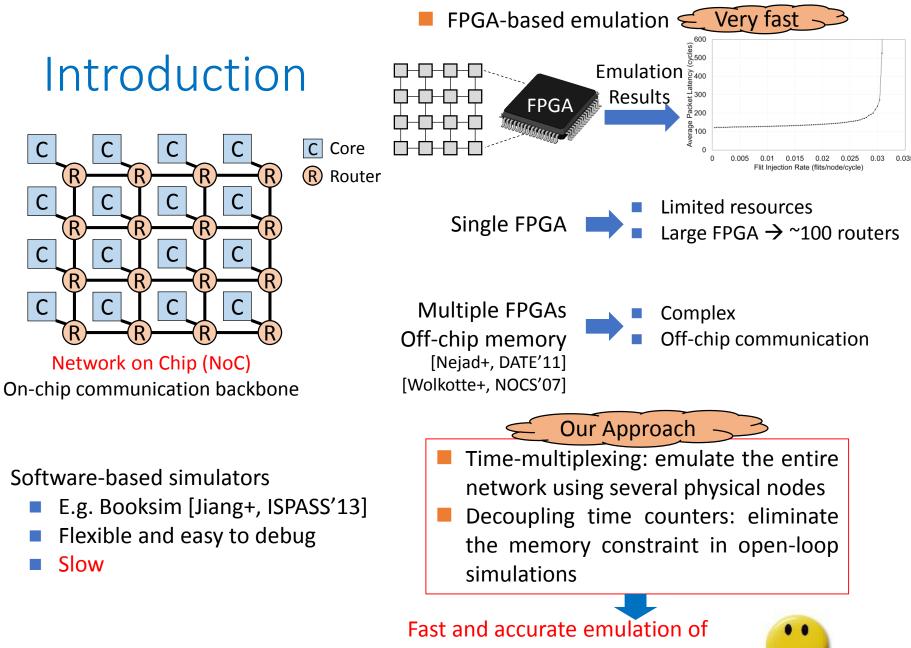

### Enabling Fast and Accurate Emulation of Large-scale Network on Chip Architectures on a Single FPGA

Thiem Van Chu<sup>1)</sup>, Shimpei Sato<sup>2)</sup>, and Kenji Kise<sup>1)</sup>

#### <sup>1)</sup>Tokyo Institute of Technology

<sup>2)</sup>Japan Advanced Institute of Science and Technology

large NoC designs on a single FPGA

2

# Key ideas

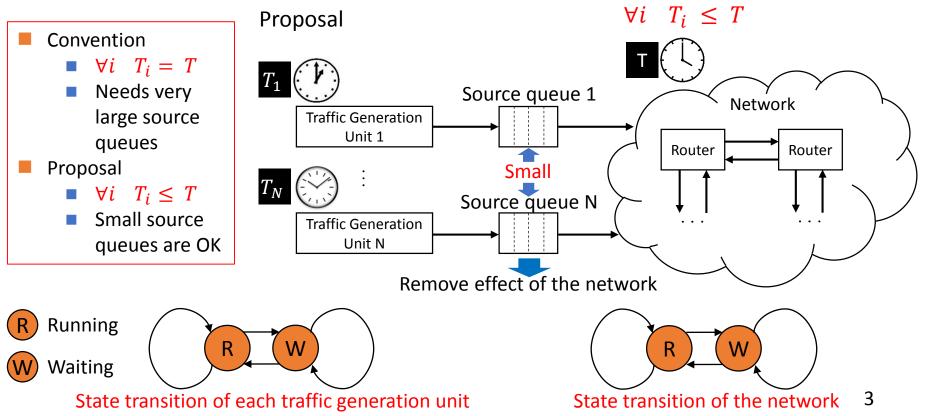

#### **Time-multiplexing**

#### Decoupling time counters

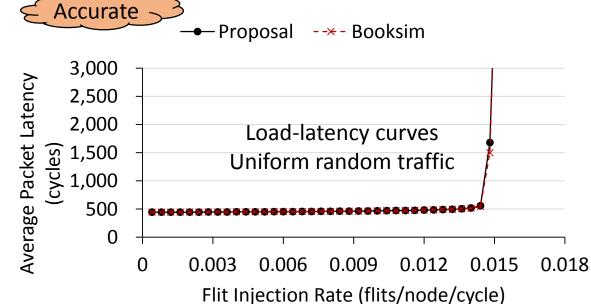

### Evaluation

128x128 mesh network (16,384 nodes)

Conventional 5-stage pipelined router architecture (2VCs/port)

**FPGA**

Virtex-7 FPGA

Booksim: > 162 hours

# Conclusion

We propose two methods to enable fast and accurate emulation of large-scale NoC architectures on a single FPGA

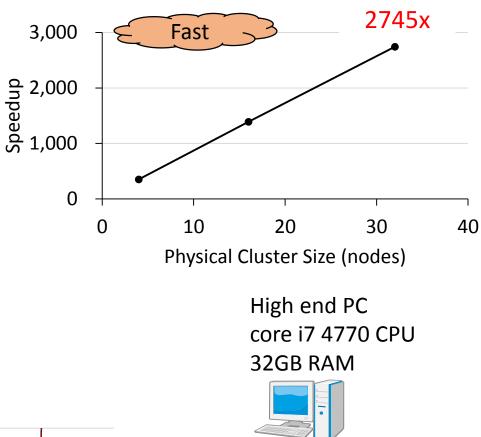

**2745x simulation speedup over Booksim** is achieved when emulating an 128x128 NoC design with the state-of-the-art 5-stage pipelined router architecture