# cloudFPGA

**Promoting FPGAs to become** 1<sup>st</sup> class-citizens in datacenters

Workshop: "The Future of FPGA-Acceleration in Cloud and Datacenters", FCCM 2020, May 6

### Prologue – What are we trying to solve?

### Goal → Deploy FPGAs at <u>large scale</u> in hyperscale DCs ↓ 1-10s of thousands per DC

Requirements

- Server commodity & homogeneity

- Decrease in cost and power

- Easy to manage and to deploy

- On-demand acceleration

- High utilization + workload migration

- Security, virtualization, orchestration

- Hybrid  $\rightarrow$  public & private

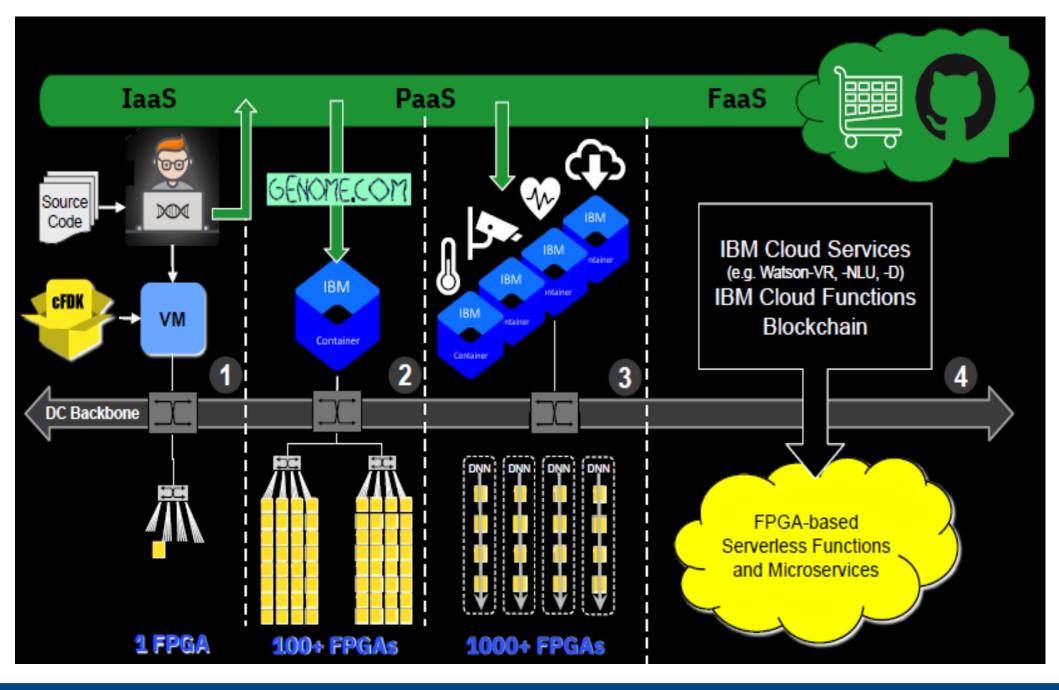

- Flexible  $\rightarrow$  IaaS, PaaS, FaaS

- Clusters  $\rightarrow$  #accelerators per server

- Community  $\rightarrow$  #APPs, # developers

### Prologue – What are we trying to solve?

# Goal → Deploy FPGAs at <u>large scale</u> in hyperscale DCs ♀ 1-10s of thousands per DC

Requirements

$-H_{\rm V}$

- Server commodity & homogeneity

- Decrease in cost ower

- deploy - Easy to m

- Scale Game Fully driven by the perf-per-cost metric migration

- orchestration s private

- Flex laaS, PaaS, FaaS

- Clusters  $\rightarrow$  #accelerators per server

- Community  $\rightarrow$  #APPs, # developers

### cloudFPGA – A bird's eye view

- Architecture & Design choices

- HW: Boards, SLEDs, chassis

- SW: Shell, Role, Management core

- DC : Resource manager

### How-to cloudFPGA @ ZYC2

## Future work & Call for contribution

# cloudFPGA

# A bird's eye view

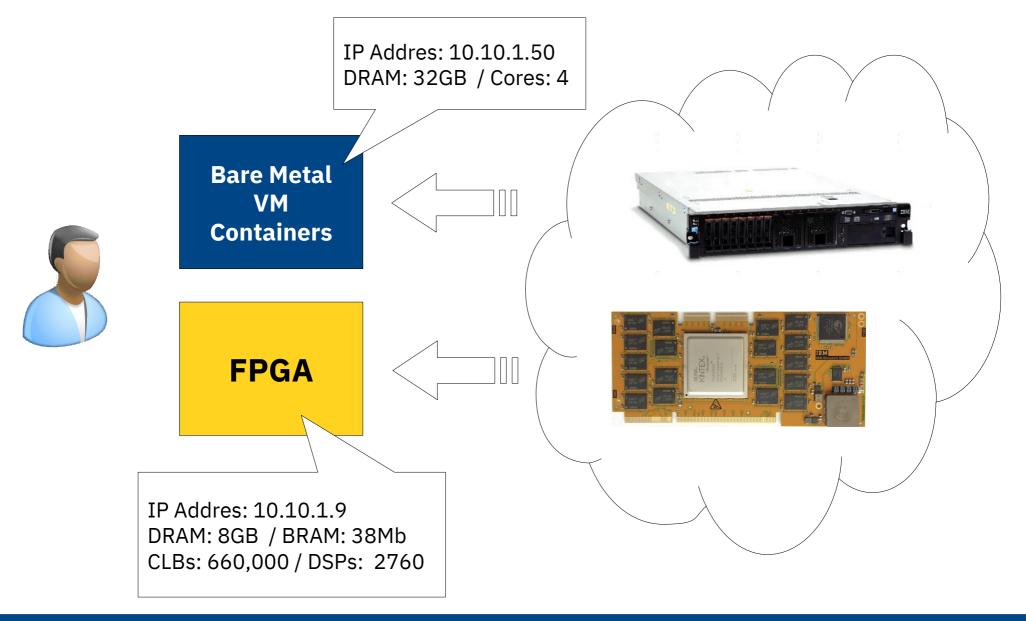

### cloudFPGA in few words

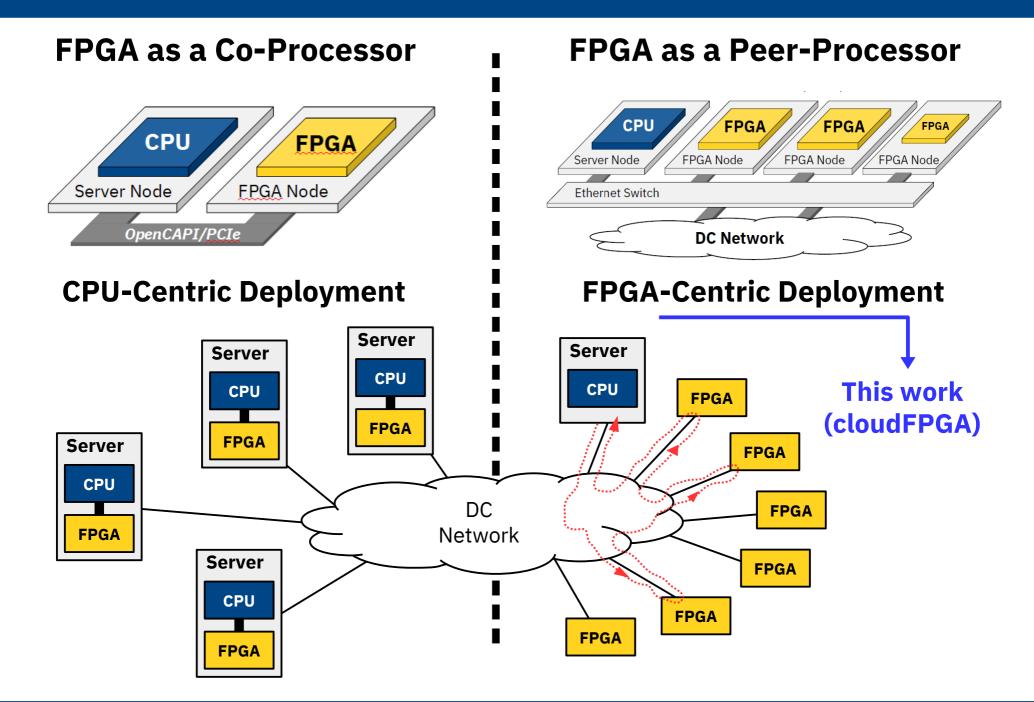

- End of CPU slavery [3]

FPGAs becomes the compute node

- Standalone operation [4]

Disaggregated from CPU servers

Fast power-on / power-off

- Network-attached [5]

TCP-UDP / IP / Ethernet (currently 10-40GE)

Leaf-spine design

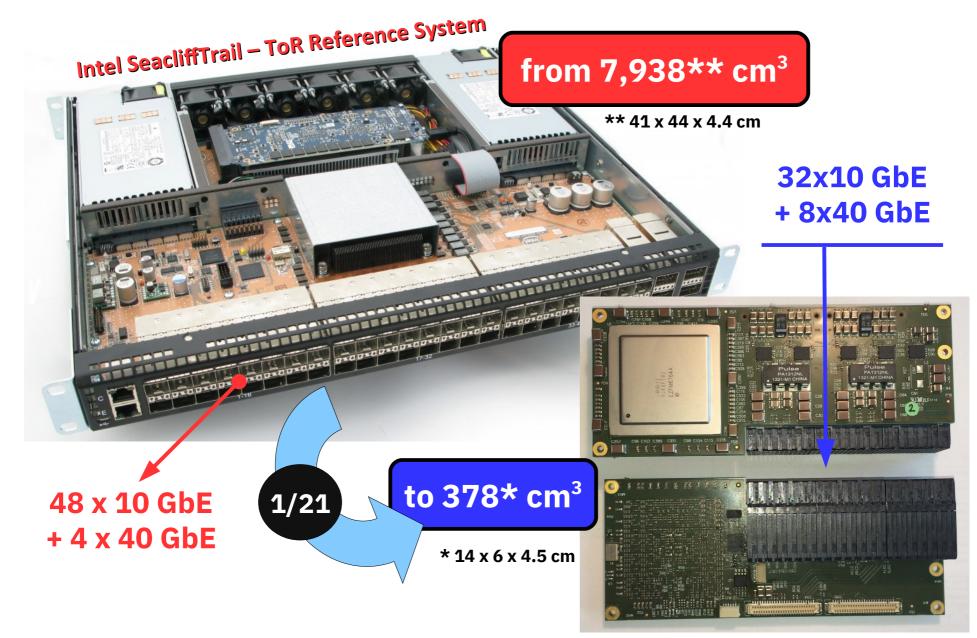

- Hyperscale infrastructure [6]

Focus on cost, energy, density, scalability

Promotes the use of mid-range FPGAs

### cloudFPGA in few words

- End of CPU slavery [3]

FPGAs becomes the compute node

- Standalone operation [4]

Disaggregated from CPU servers

Fast power-on / power-off

- Network-attached [5]

TCP-UDP / IP / Ethernet (currently 10-40GE)

Leaf-spine design

- Hyperscale infrastructure [6]

Focus on cost, energy, density, scalability

Promotes the use of mid-range FPGAs

### FPGAs to become 1<sup>st</sup> class-citizens in DC-Cloud

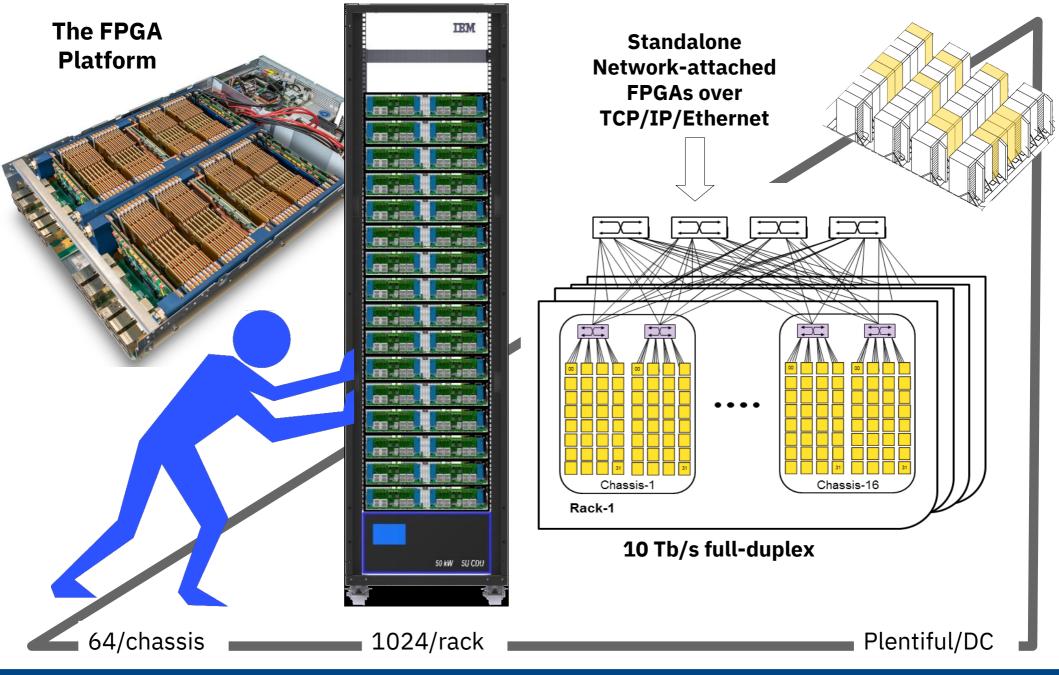

### DC Vision = Hyperscale Infrastructure

### Cloud Vision = IaaS, PaaS, FaaS

### Architecture & Design choices HW: Boards, SLEDs, chassis

### Standalone $\rightarrow$ The FPGA becomes the node

### Disaggregation of the FPGA from the server

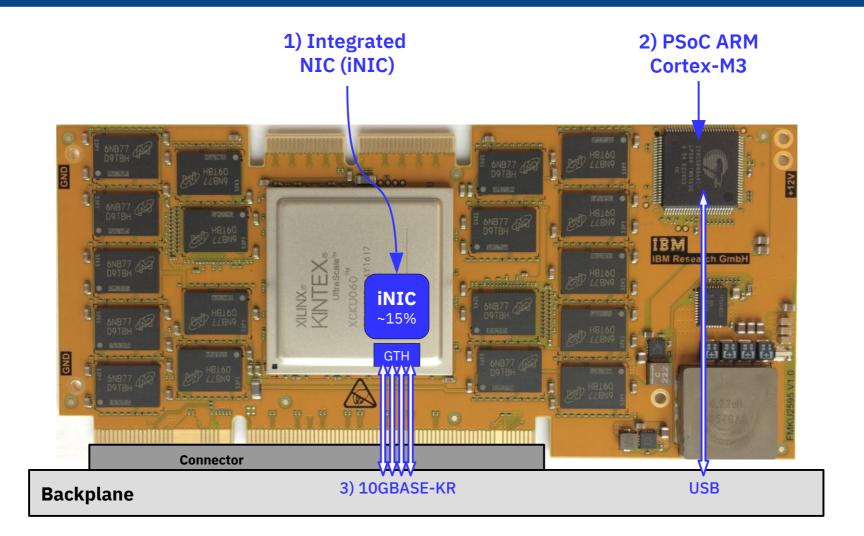

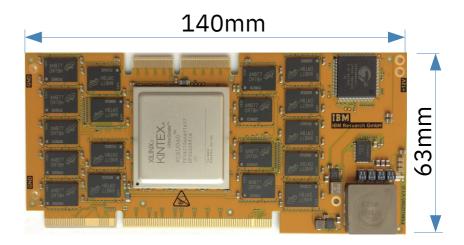

### Standalone network-attached FPGA

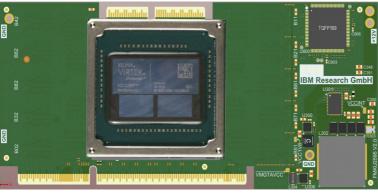

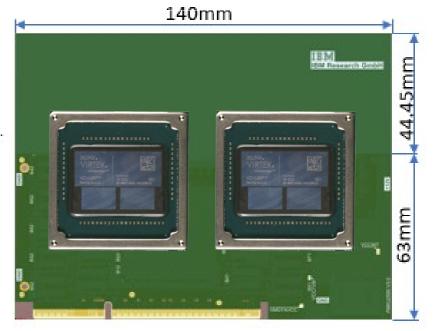

- 1) Replace PCIe I/F with integrated NIC (iNIC)

- 2) Turn FPGA card into a standalone resource

- 3) Replace transceivers w/ backplane connectivity

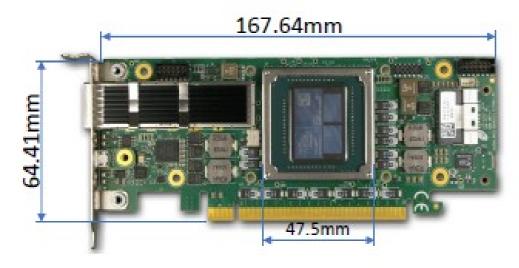

### How does it compare w/ PCIe cards?

For comparison: ALPHA DATA ADM-PCIE-9H3, 1/2 Length, low profile, x16 PCIe form Factor

Figurative picture

**Figurative picture**

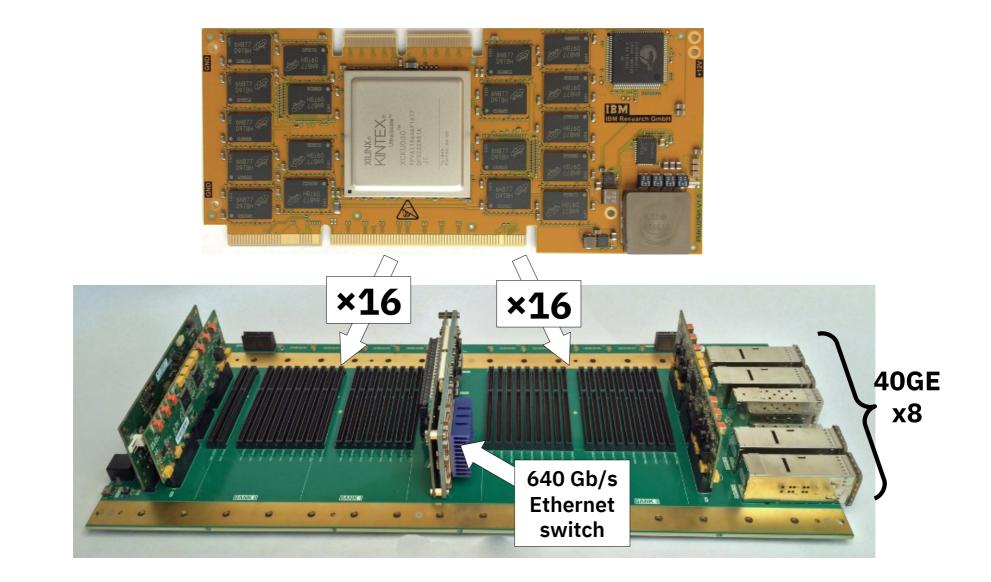

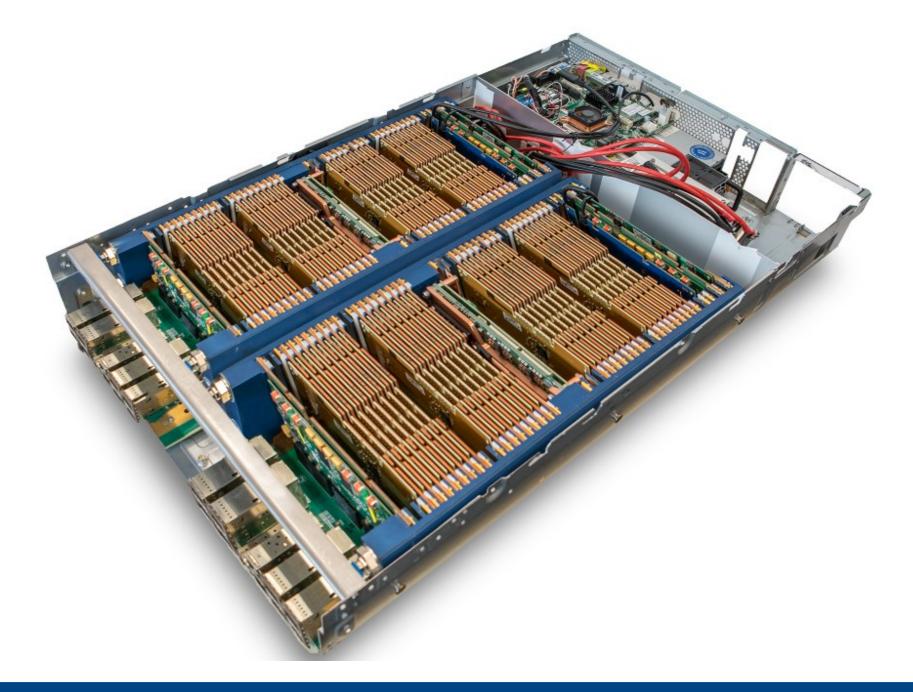

### One carrier SLED (a.k.a PoD)= 32 FPGA modules

### From top-of-rack down to SLED/PoD switch

Switch Module SM6000

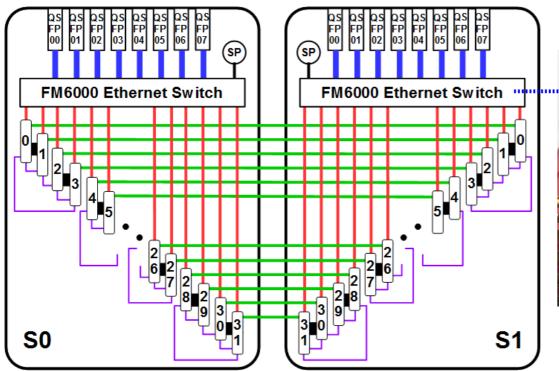

### Network topology per chassis = 64 FPGAs

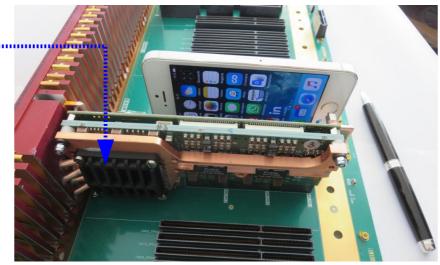

Integration size scale: Ethernet switch FM6000 (64x10GbE) vs iPhone5

Legend (per slice): x840GbE up links(320 Gb/s)Balanced (i.e. no over-subscription)-] x3210GbE FPGA-to-Switch links(320 Gb/s)Balanced (i.e. no over-subscription)between the north and south links of the Ethernet switch [==] x32 10GbE redundant links x32 10GbE FPGA-to-FPGA links x16 PCIe x8 Gen3 SP x1 Service Processor

### The cloudFPGA Platform (19"x2U w/64 FPGAs)

### Architecture & Design choices SW: Shell, Role, Mngt core

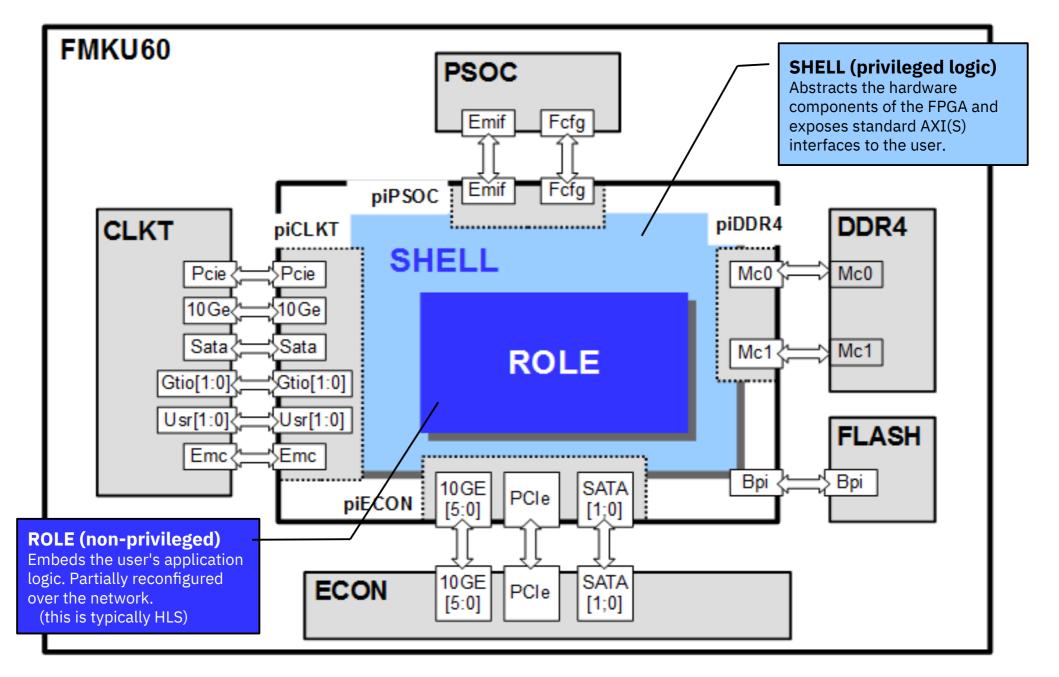

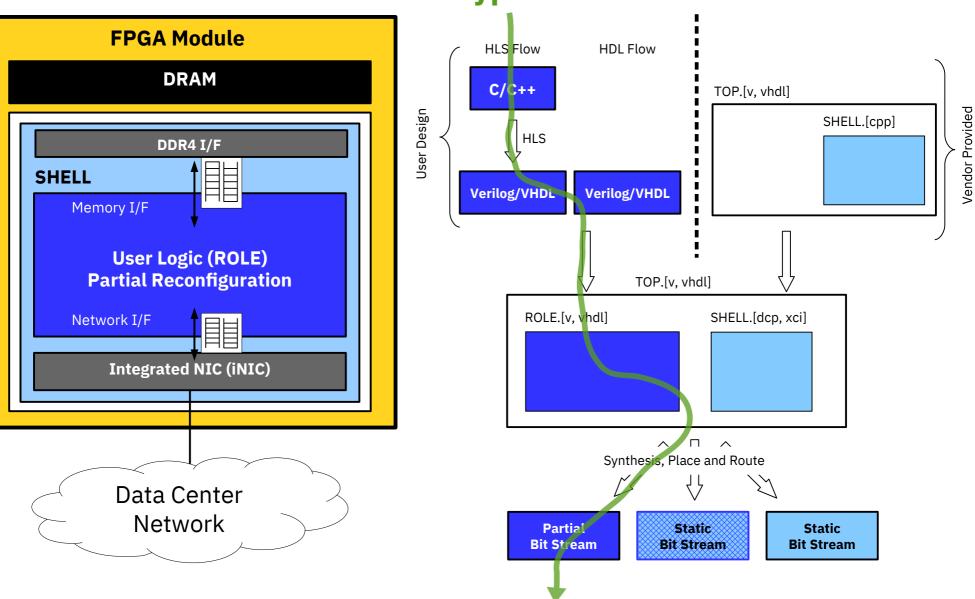

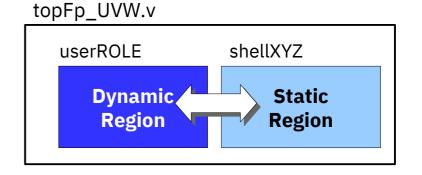

### Hw Abstraction → Shell Role Architecture (SRA)

### cloudFPGA Development Kit (cFDK)

### **Typical HLS flow**

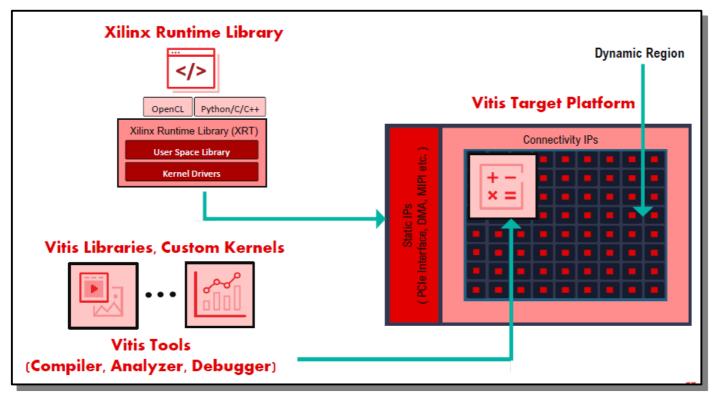

## Analogy with Vitis target platforms

Source: Development with Vitis Accelerated Libraries, Xilinx 2020

- cF-SHELL → Static Region → Privileged logic → Configured after power-on via local Flash.

- **cF-ROLE** → Dynamic Region → Nonprivileged logic → Partially configured over the network.

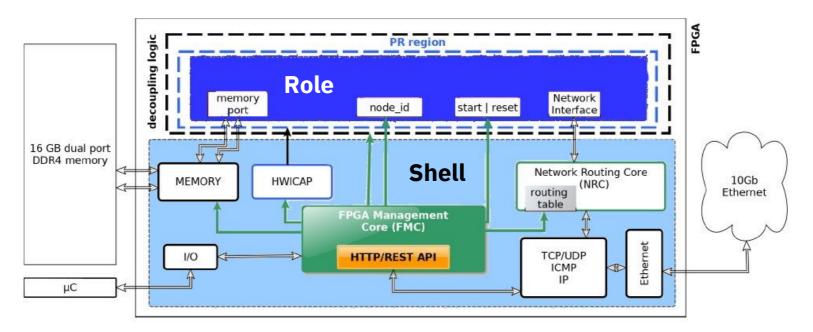

### **FPGA Management Core**

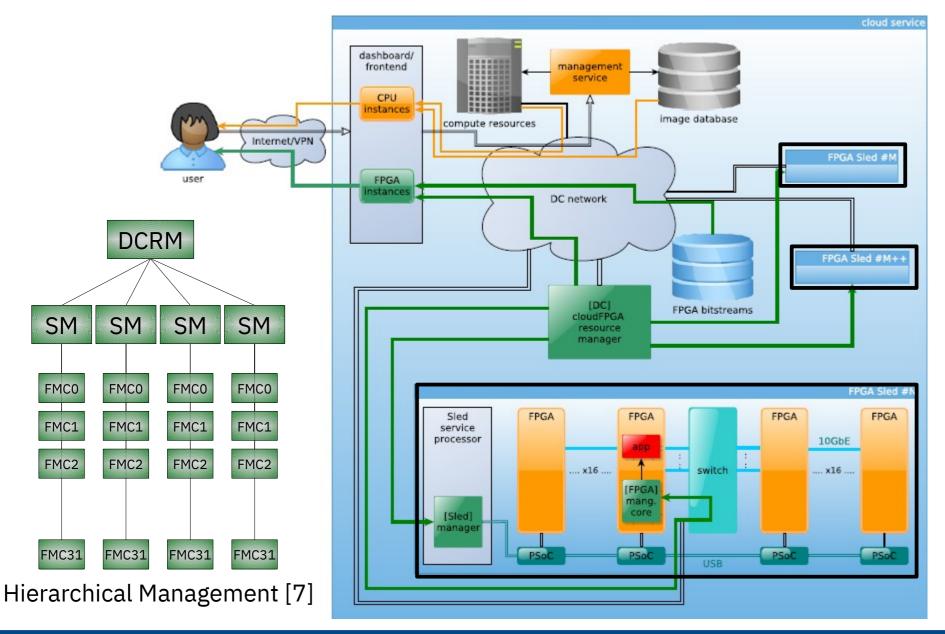

### There is one management core per FPGA (FMC)

- The FMC contains a simplified HTTP server which provides support for the REST API calls issued by the Data Center Resource Manager (DCRM) [7].

The FMC understands REST API calls such as:

- POST /configure Submits a partial bitfile and triggers the PR of the Role region.

- GET /status Returns some application-specific status information.

- PUT /node\_id Sets the node-id register of the Role.

- POST /routing Sends the routing information of a cluster to the FPGA.

### Architecture & Design choices DC: Resource manager

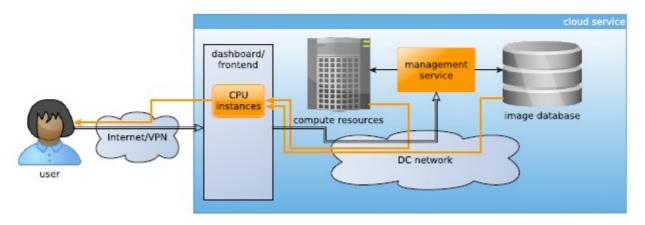

### Cloud Service Architecture for FPGAs (1/2)

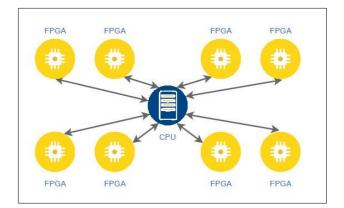

# Instance = Resource + Image Cluster = N \* Instance

A typical cloud service hosting VMs has three components:

- A pool of compute resources

- A database of VM images

- A management service

### Cloud Service Architecture for FPGAs (2/2)

### Instance = FPGA + Bitstream

### **RESTful Web API Based**

| cloudFPGA Resource Manaç             |                                             |                                                |

|--------------------------------------|---------------------------------------------|------------------------------------------------|

| Clusters                             | Show/Hide List Operations Expand Operations |                                                |

| mages                                | ShowHide List Operations Expand Operations  |                                                |

| get limages                          | Get all user images                         |                                                |

| Post /images                         | Upload an image                             |                                                |

| ELETE /images/{image_id}             | Delete an image                             |                                                |

| GET /images/{image_id}               | Get an image                                |                                                |

| nstances                             | cloudFPGA Resource Manager API              |                                                |

| esources                             | oloudi i oz resource manager zi i           |                                                |

| GET /resources                       | Clusters                                    | Show/Hide List Operations Expand Operation     |

| vost /resources                      | GET /clusters                               | Get all user cluste                            |

| ccr /resources/status/{status}       | Post /clusters                              | Request a clust                                |

| clete /resources/{resource_id}       |                                             | Delete a clust                                 |

| cct /resources/{resource_id}         | DELETE /clusters/{cluster_id}               | Deste a cluss                                  |

| PUT /resources/{resource_id}         | GET /clusters/{cluster_id}                  | Get a clust                                    |

| GET /resources/{resource_id}/status/ | Images                                      | Show/Hide   List Operations   Expand Operation |

| PUT /resources/(resource_id)/status/ | Instances                                   | Show/Hide List Operations Expand Operation     |

| BASE URL: / , API VERSION: 0.2 ]     | GET /instances                              | Get all instance                               |

|                                      | Post Jinstances                             | Create an instance                             |

|                                      | DELETE /instances/{instance_id}             | Remove an Instance                             |

|                                      | GET /instances/{instance_id}                | Get a single instand                           |

|                                      | Resources                                   | Show/Hide List Operations Expand Operation     |

|                                      | [ BASE URL: / , API VERSION: 0.2 ]          |                                                |

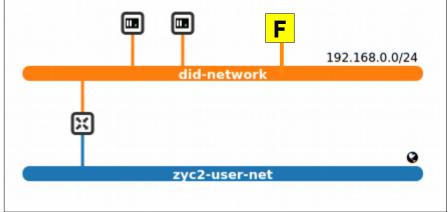

\*On-premise deployment in the Zurich Yellow security zone Compute Cluster

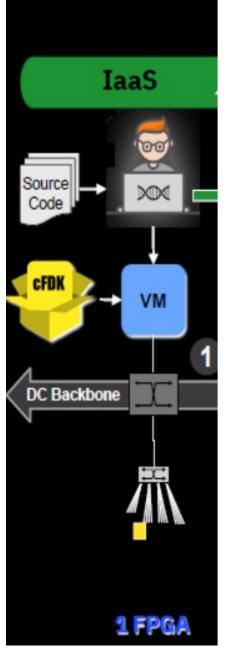

## Example #1 – "Hello, World!" with a single FPGA

- 1) Download the cFDK to work remotely on your desktop or use a VM @ ZYC2

- 2) Setup a VPN client, create an OpenStack project and a private network for it

- 3) Develop and simulate

- 4) Place and route

- 5) Upload your bitstream

- You'll receive an *image-id*

6) Request an instance to be launched with your *image-id*

– You'll get back an *image-IP* and an *instance-id*

### 7) Ping the *image-IP*

8) You are ready to communicate with your FPGA via network sockets with TCP or UDP protocol

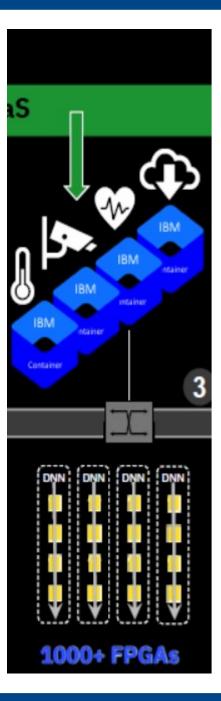

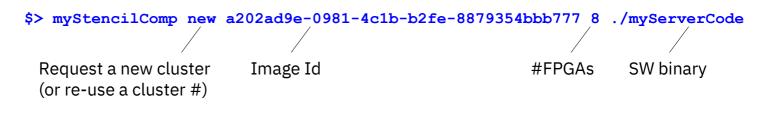

# Example #2 – "Stencil comp." → 1 HOST + 8 FPGAs

#### 1) Design your FPGA kernel(s) and your HOST code

```

while ((not converged) and (max iterations not reached)) {

for (i, j) distribute over all nodes {

if(i is border or j is border)

continue;

xnew[i][j] = (x[i+1][j] + x[i-1][j] + x[i][j+1] + x[i][j

-1])/4;

}

for (i, j)  # done on one node

x[i][j] = xnew[i][j];

}

```

### 2) Build, place and route

3) Use a script to interact with the RESTfull Web API

- Upload the bitstream(s)

- Request a cluster to be launched

- Let the HOST send and receive to/from the FPGAs

FYI, see also [8]: A one-click solution which compiles a standard MPI application for a Reconfigurable Heterogeneous Computing Cluster (ReH<sup>2</sup>PC).

### Future Work (1/2)

### 1) Open-source the cloudFPGA Development Kit (cFDK)

- Coming soon

- Give the research community access to cloudFPGA platform

### 2) Walking up the application stack

- Lower-precision inference and autoML

- Support for Vitis accelerated libraries

- Large-scale distributed applications

- Support popular programming languages and frameworks

### 3) Walking up the systems stack

- Function-as-a-Service (aka Serverless computing)

- Composable and disaggregated storage (NVMe-oF)

- Lighter and faster network protocols

### Future Work (2/2)

### 4) Expand the numbers of Xilinx-based modules

- Produce a stronger FPGA module (e.g. XCVU33P w/ HBM)

- Produce a module with an MPSoC or a Versal ACAP

### 5) Support faster link technologies

– 25GE, 100GE

### 6) Support other FPGA vendors

– Intel, Achronix, ...

### 7) Share the cloudFPGA platform design (e.g. à la OCP)

### The cloudFPGA suspects

#### Current team

Francois

Mark

Raphael

#### Former contributors

Alex

Andreas

Mitra

Ron

#### Stephan

### Summary

### 1) FPGAs are eligible to become 1<sup>st</sup> class citizens

- Standalone approach sets the FPGA free from the CPU

- Large scale deployment of FPGAs independent of #servers

- Significantly lowers the entry barrier

- Promotes the use of medium and low-cost FPGAs

### 2) The network-attachment model

- Makes FPGAs IP-addressable and scalable in DCs

- Users can rent and link them in any type of topology

- Opens the path for use of FPGAs in large scale applications

- Serverless computing, HPC, DNN inference, Signal Processing, ...

### 3) The hyperscale infrastructure

- Integrates FPGAs at the chassis (aka drawer) level

- Combines passive and active water cooling

- Key enabler for FPGAs to become plentiful in DCs

# Thank you

# May the FPGA be with you

https://www.zurich.ibm.com/cci/cloudFPGA/

[8] B. Ringlein, F. Abel, A. Ditter, B. Weiss, C. Hagleitner and D. Fey,

"ZRLMPI: A Unified Programming Model for Reconfigurable Heterogeneous Computing Clusters" in 28th International Symposium On Field-Programmable Custom Computing Machines (FCCM), 2020.

[7] B. Ringlein, F. Abel, A. Ditter, B. Weiss, C. Hagleitner and D. Fey,

"System architecture for network-attached FPGAs in the cloud using partial reconfiguration," in 29th International Conference on Field Programmable Logic and Applications (FPL), 2019.

[6] F. Abel, J. Weerasinghe, C. Hagleitner, B. Weiss, S. Paredes,

"An FPGA Platform for Hyperscalers," in IEEE 25th Annual Symposium on High-Performance Interconnects (HOTI), Santa Clara, CA, pp. 29–32, 2017.

[5] J. Weerasinghe, F. Abel, C. Hagleitner, A. Herkersdorf,

"Disaggregated FPGAs: Network performance comparison against bare-metal servers, virtual machines and Linux containers," in IEEE International Conference on Cloud Computing Technology and Science (CloudCom), Luxembourg, 2016.

[4] J. Weerasinghe, R. Polig, F. Abel,

"Network-attached FPGAs for data center applications," in IEEE International Conference on Field-Programmable Technology (FPT '16), Xian, China, 2016.

[3] J. Weerasinghe, F. Abel, C. Hagleitner, A. Herkersdorf,

"Enabling FPGAs in hyperscale data centers," in IEEE International Conference on Cloud and Big Data Computing (CBDCom), Beijing, China, pp. 1078–1086, 2015.

[2] F. Abel,

"How do you squeeze 1000 FPGAs into a DC rack?" online at LinkedIn

[1] The cloudFPGA project page at ZRL

https://www.zurich.ibm.com/cci/cloudFPGA/